| –≠–ª–µ–∫—Ç—Ä–æ–Ω–Ω—ã–π –∫–æ–º–ø–æ–Ω–µ–Ω—Ç: ICX252 | –°–∫–∞—á–∞—Ç—å:  PDF PDF  ZIP ZIP |

CXD3406GA

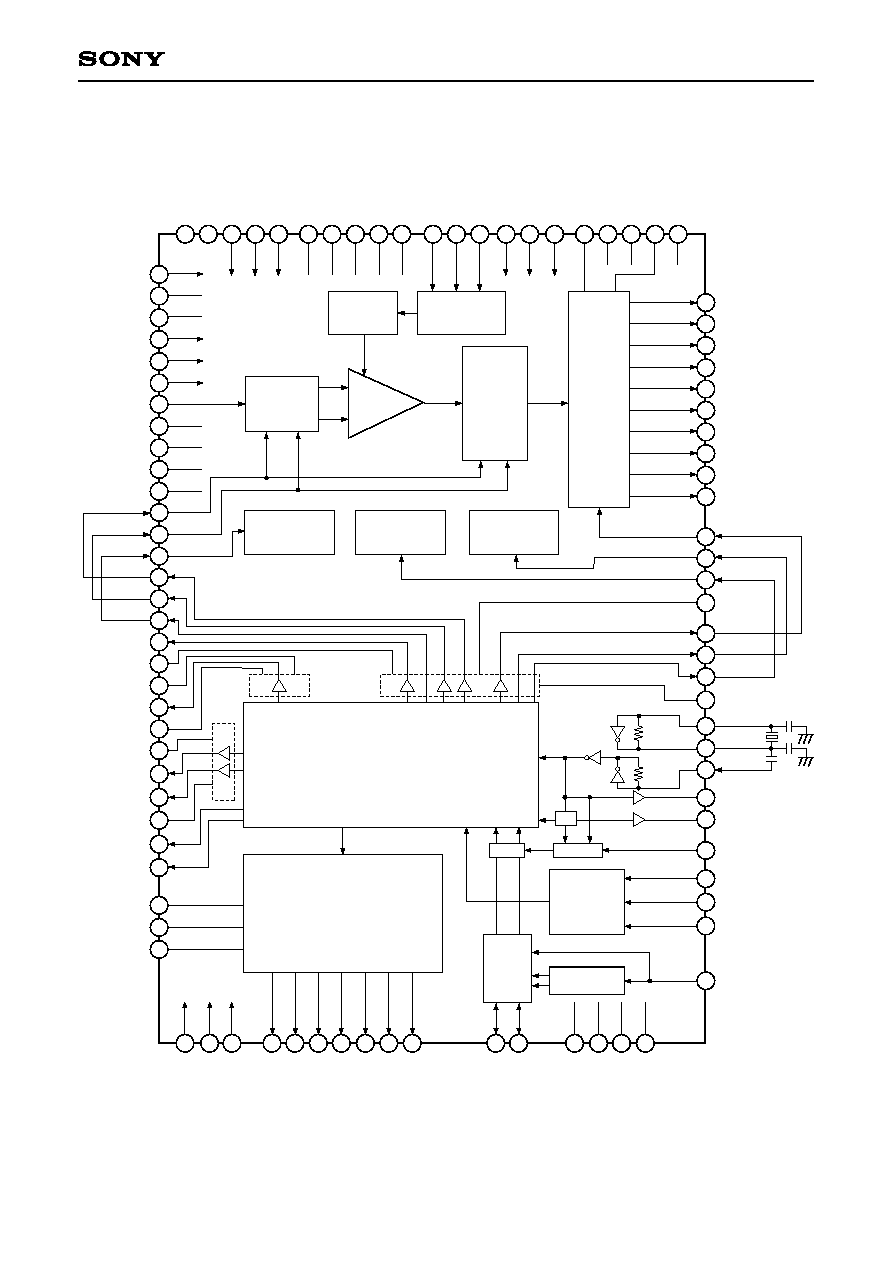

Timing Generator and Signal Processor for Frame Readout CCD Image Sensor

Description

The CXD3406GA is a timing generator and CCD

signal processor IC for the ICX252/262 CCD image

sensor.

Features

∑ Timing generator functions

∑ Horizontal drive frequency 12 to 18MHz

(Base oscillation frequency 24 to 36MHz)

∑ Supports frame readout/draft (sextuple speed)/

AF (Auto focus drive)

∑ High-speed/low-speed shutter function

∑ Horizontal and vertical drivers for CCD image

sensor

∑ CCD signal processor functions

∑ Correlated double sampling

∑ Programmable gain amplifier (PGA) allows gain

adjustment over a wide range (≠6 to +42dB)

∑ 10-bit A/D converter

∑ Chip Scale Package (CSP):

CSP allows vast reduction in the CCD camera

block footprint

Applications

Digital still cameras

Structure

Silicon gate CMOS IC

Applicable CCD Image Sensors

ICX252 (1/1.8", 3240K pixels)

ICX262 (1/1.8", 3240K pixels)

Absolute Maximum Ratings

∑ Supply voltage

V

DD

a, V

DD

b, V

DD

c, V

DD

d

V

SS

≠ 0.3 to +7.0

V

V

DD

e, V

DD

f, V

DD

g

V

SS

≠ 0.3 to +4.0

V

VL

≠10.0 to V

SS

V

VH

VL ≠ 0.3 to +26.0

V

∑ Input voltage (analog)

V

IN

V

SS

≠ 0.3 to V

DD

+ 0.3

V

∑ Input voltage (digital)

V

I

V

SS

≠ 0.3 to V

DD

+ 0.3

V

∑ Output voltage

V

O1

V

SS

≠ 0.3 to V

DD

+ 0.3

V

V

O2

VL ≠ 0.3 to V

SS

+ 0.3

V

V

O3

VL ≠ 0.3 to VH + 0.3

V

∑ Operating temperature

Topr

≠20 to +75

∞C

∑ Storage temperature

Tstg

≠55 to +125

∞C

Recommended Operating Conditions

∑ Supply voltage

V

DD

b

3.0 to 5.5

V

V

DD

a, V

DD

c, V

DD

d

3.0 to 3.6

V

VM

0.0

V

VH

14.5 to 15.5

V

VL

≠7.0 to ≠8.0

V

V

DD

e, V

DD

f, V

DD

g

3.0 to 3.6

V

∑ Operating temperature

Topr

≠20 to +75

∞C

≠ 1 ≠

E00Z02A26

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

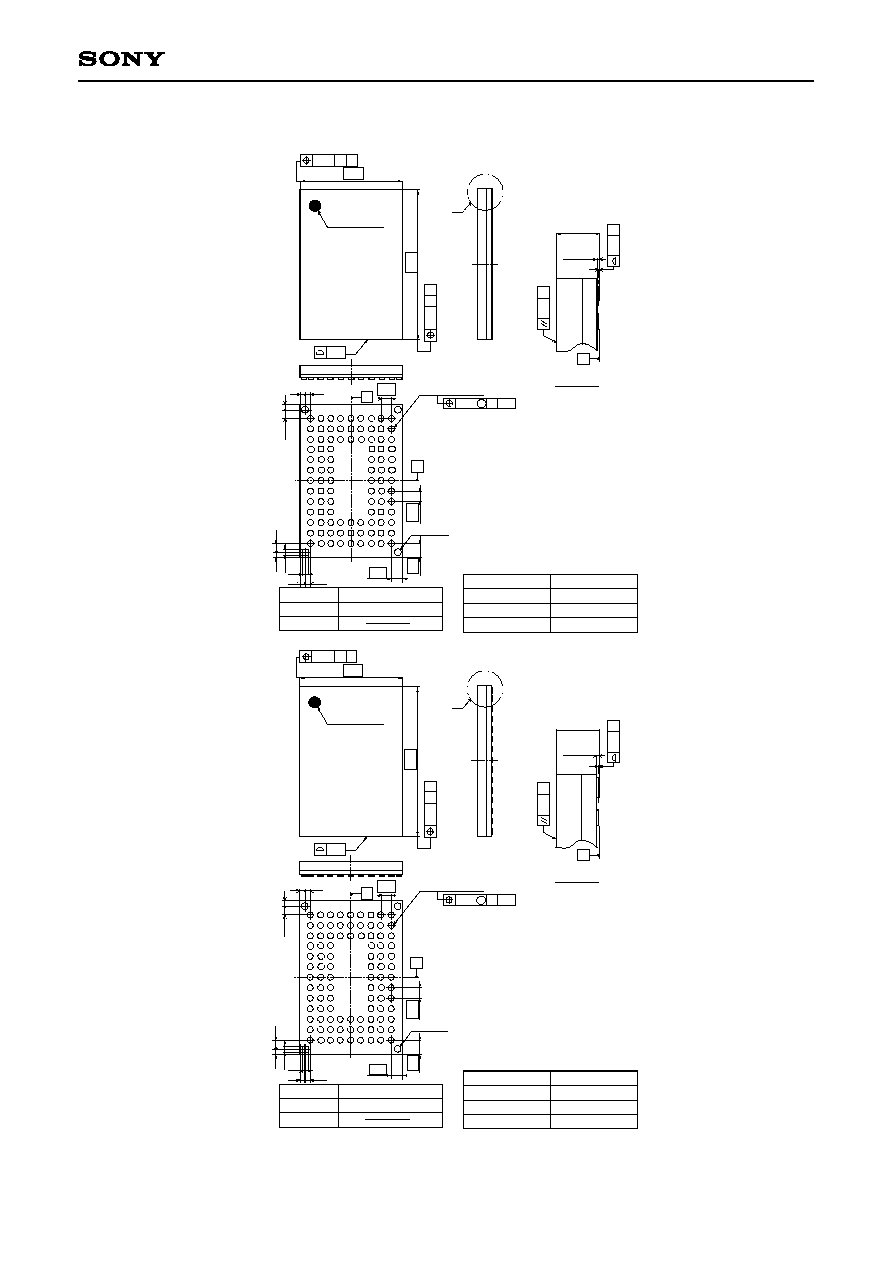

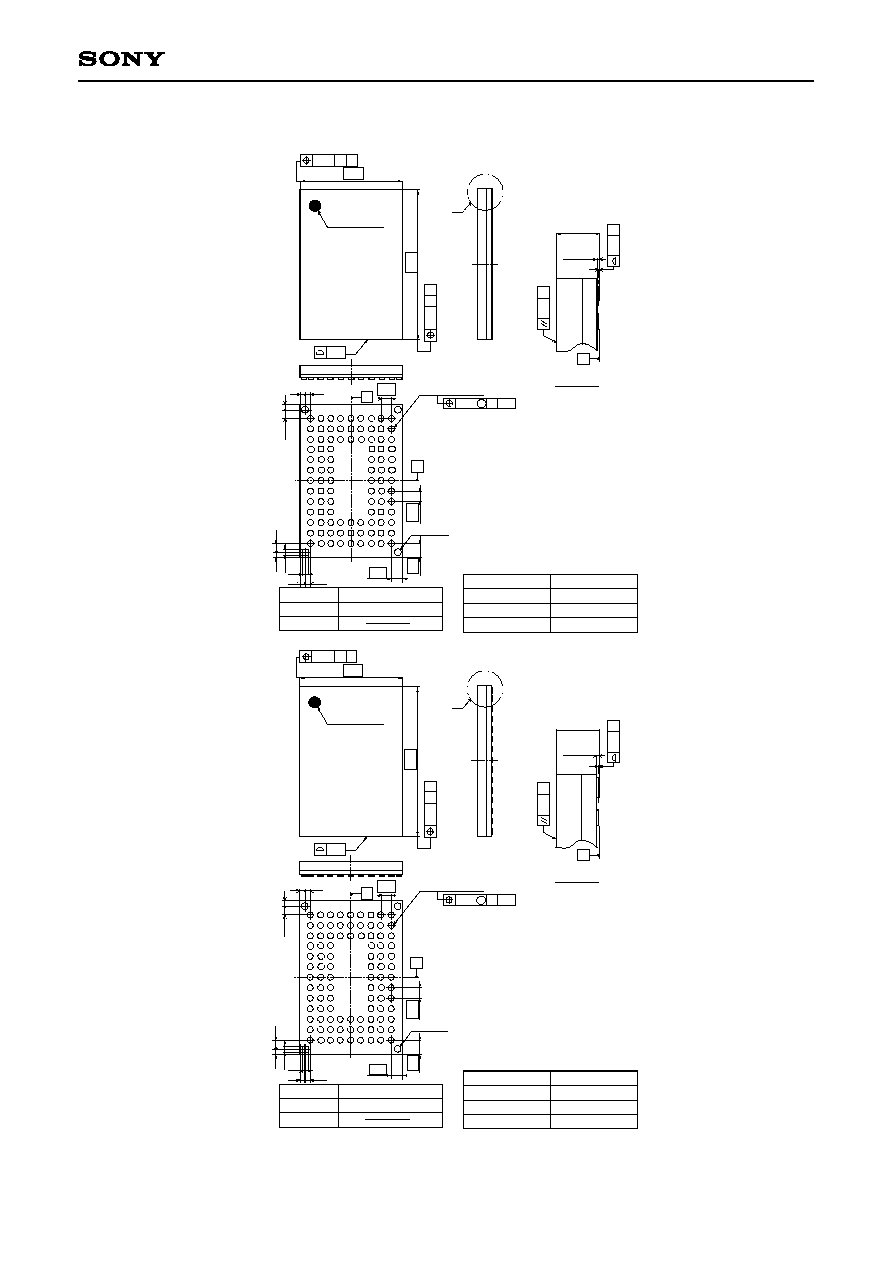

96 pin LFLGA (Plastic)

≠ 2 ≠

CXD3406GA

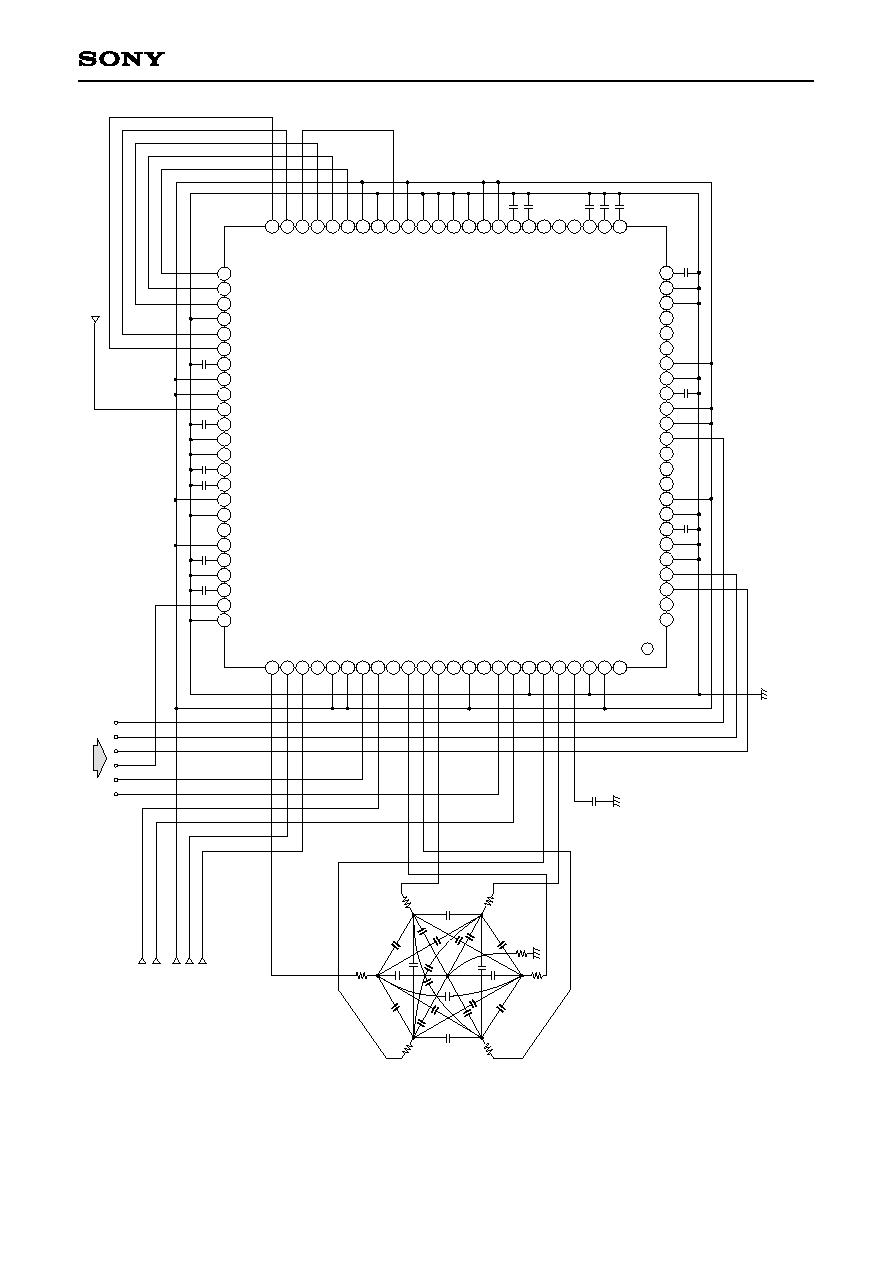

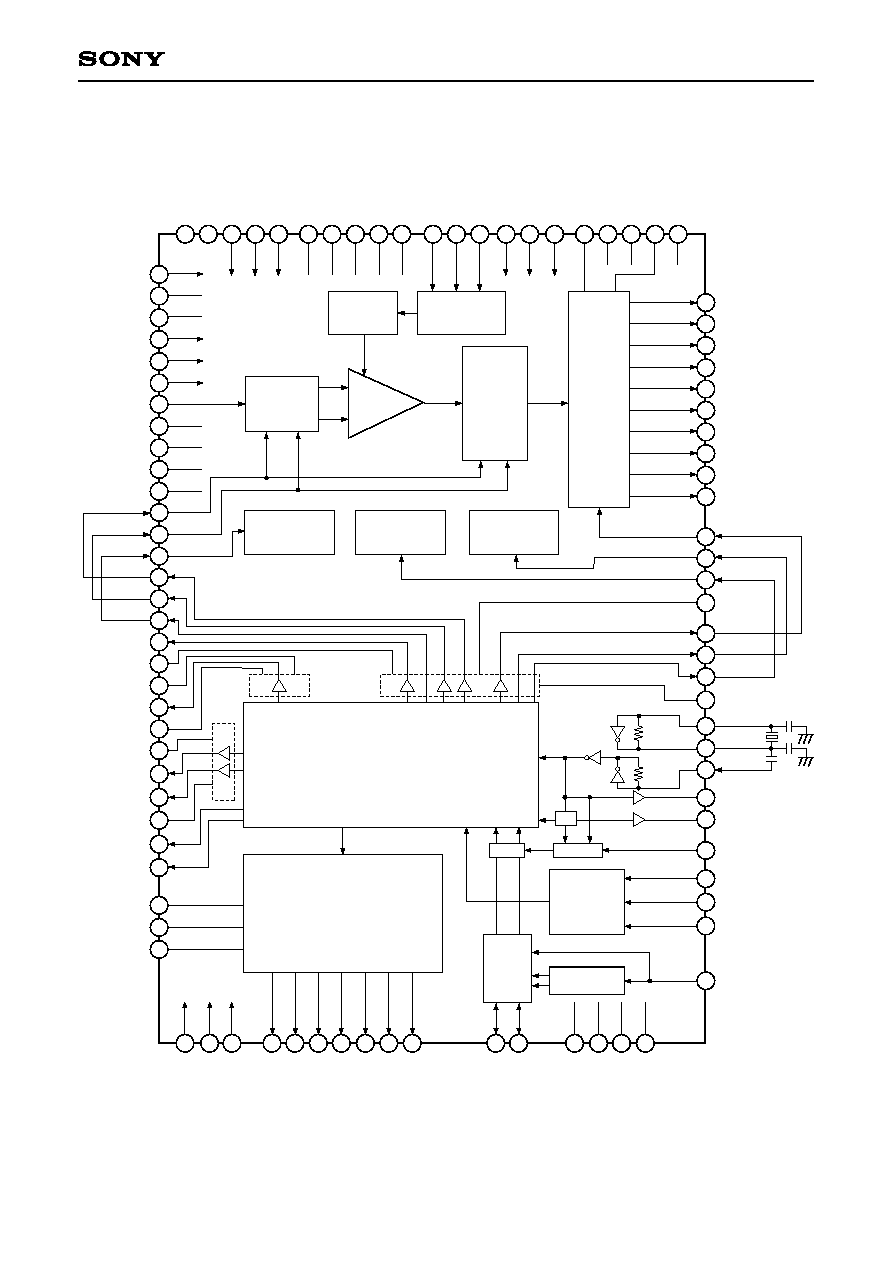

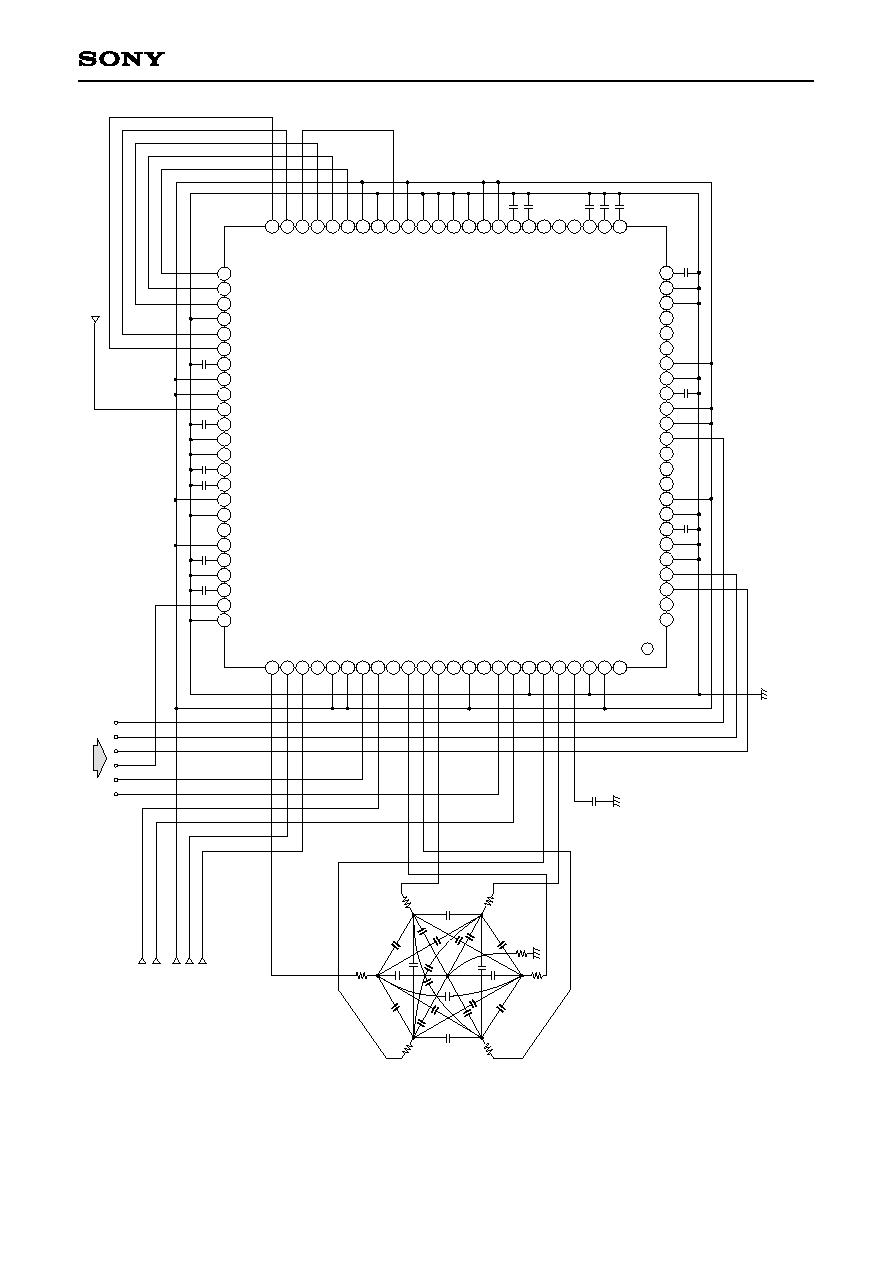

Block Diagram

C7

C3

A1

NC

A2

NC

D8

C2

D7

C1

B8

AV

DD3

B6

AV

DD4

B9

AV

SS3

A6

AV

SS4

C5

AV

SS5

A3

SCK2

A4

SSI2

B4

SEN2

A5

TEST3

C4

TEST4

B5

TEST5

E2

DV

DD1

F2

DV

SS3

F3

DV

DD2

E3

DV

SS1

F1

B3

DV

SS2

D0 (LSB)

Latch

Serial Port

Register

DAC

PGA

CDS

ADC

Preblanking

Dummy Pixel

Auto Zero

Pulse Generator

V Driver

Serial Port

Register

Black Level

Auto Zero

B2

D1

B1

D2

C3

D3

C2

D4

C1

D5

D3

D6

D2

D7

D1

D8

E1

D9 (MSB)

G1

ADCLKI

G2

CLPOBI

G3

CLPDMI

L3

V

SS4

H1

ADCLK

H2

CLPOB

H3

CLPDM

J3

V

SS5

L1

OSCI

K1

OSCO

J1

CKI

J2

CKO

K2

MCKO

N8

SNCSL

L2

SSI1

M6

VL

L4

VM

M5

VH

M9

WEN

N9

ID

J7

V

SS3

J9

H2

J8

H1

H9

V

DD3

K9

V

SS2

K8

RG

K7

V

DD2

H8

V

DD4

H7

XRS

G7

PBLK

G8

XSHD

G9

XSHP

F7

PBLKI

F8

XSHDI

E7

AV

SS2

F9

XSHPI

D9

AV

SS1

E8

AV

DD2

E9

AV

DD1

C9

CCDIN

C6

C9

A7

C8

B7

C7

A8

AV

SS6

A9

AV

DD5

C8

C4

M1

SCK1

N1

SEN1

N3

V

SS6

L7

V

SS1

K3

V

DD5

L9

V

DD1

M2

VD

N2

HD

N7

SUB

N4

V4

N6

V3B

V3A

L6

V2

M4

N5

V1B

M7

TEST2

M3

TEST1

M8

RST

SSG

L8

SSGSL

L5

V1A

Latch

Selector

Selector

1/2

≠ 3 ≠

CXD3406GA

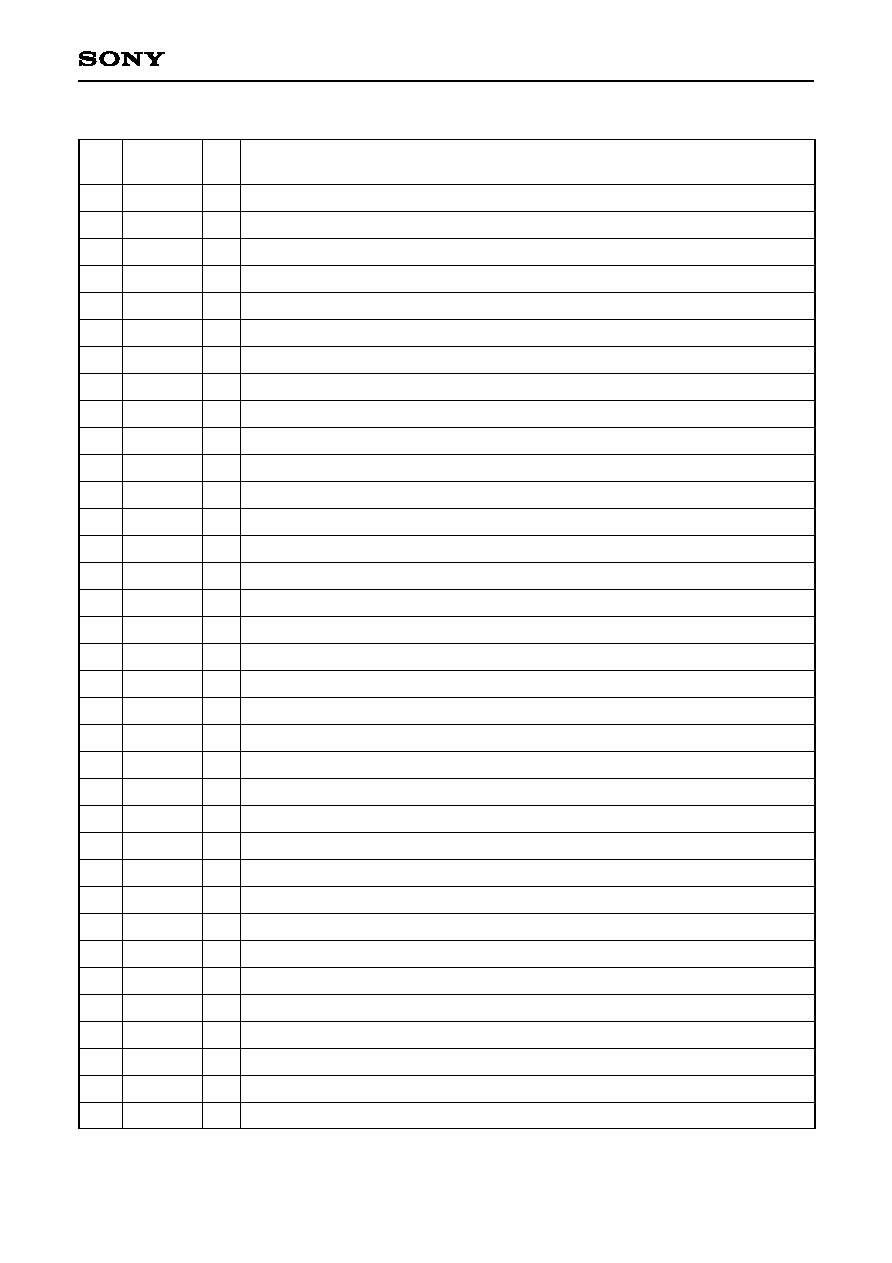

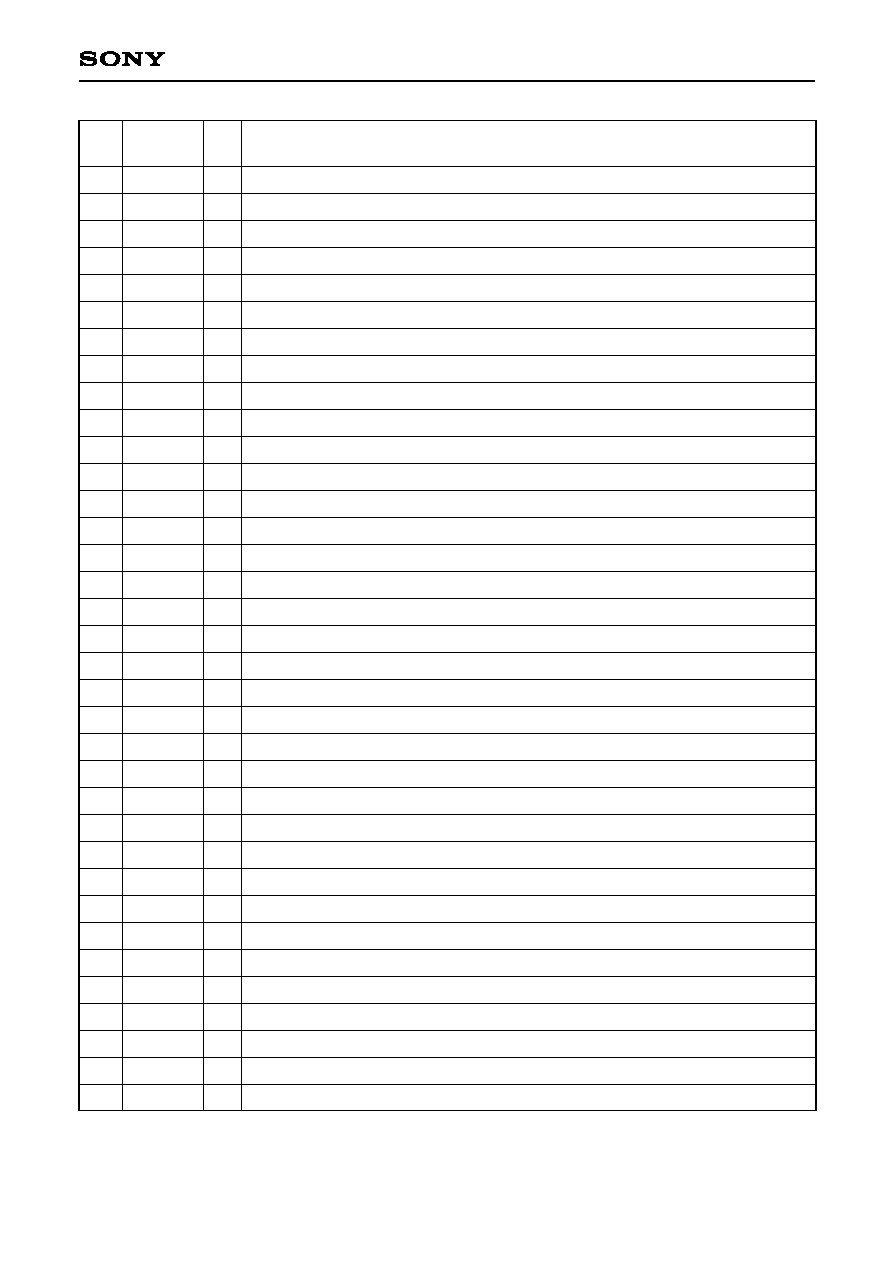

Pin Configuration (Top View)

NC

D2

D5

D8

D9

DV

SS2

ADCLKI

ADCLK

CKI

OSCO

OSCI

SCK1

SEN1

A

B

C

D

E

F

G

H

J

K

L

M

N

NC

D1

D4

D7

DV

DD1

DV

SS3

CLPOBI

CLPOB

CKO

MCKO

SSI1

VD

HD

SCK2

D0

D3

D6

DV

SS1

DV

DD2

CLPDMI

CLPDM

V

SS5

V

DD5

V

SS4

TEST1

V

SS6

SSI2

SEN2

TEST4

VM

V2

V4

TEST3

TEST5

AV

SS5

V1A

VH

V1B

AV

SS4

AV

DD4

C9

V3A

VL

V3B

C8

C7

C3

C1

AV

SS2

PBLKI

PBLK

XRS

V

SS3

V

DD2

V

SS1

TEST2

SUB

AV

SS6

AV

DD3

C4

C2

AV

DD2

XSHDI

XSHD

V

DD4

H1

RG

SSGSL

RST

SNCSL

AV

DD5

AV

SS3

CCDIN

AV

SS

1

AV

DD1

XSHPI

XSHP

V

DD3

H2

V

SS2

V

DD1

WEN

ID

1

2

3

4

5

6

7

8

9

≠ 4 ≠

CXD3406GA

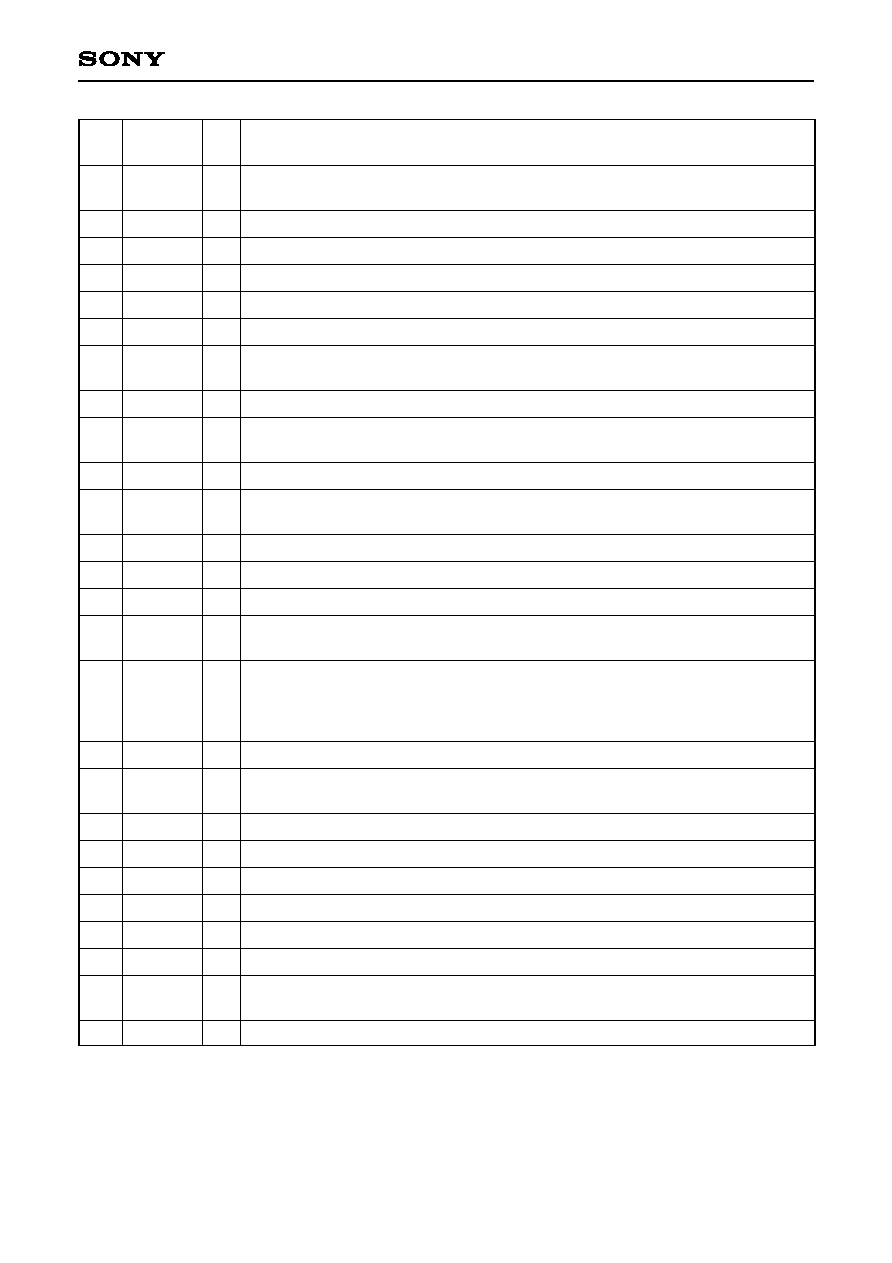

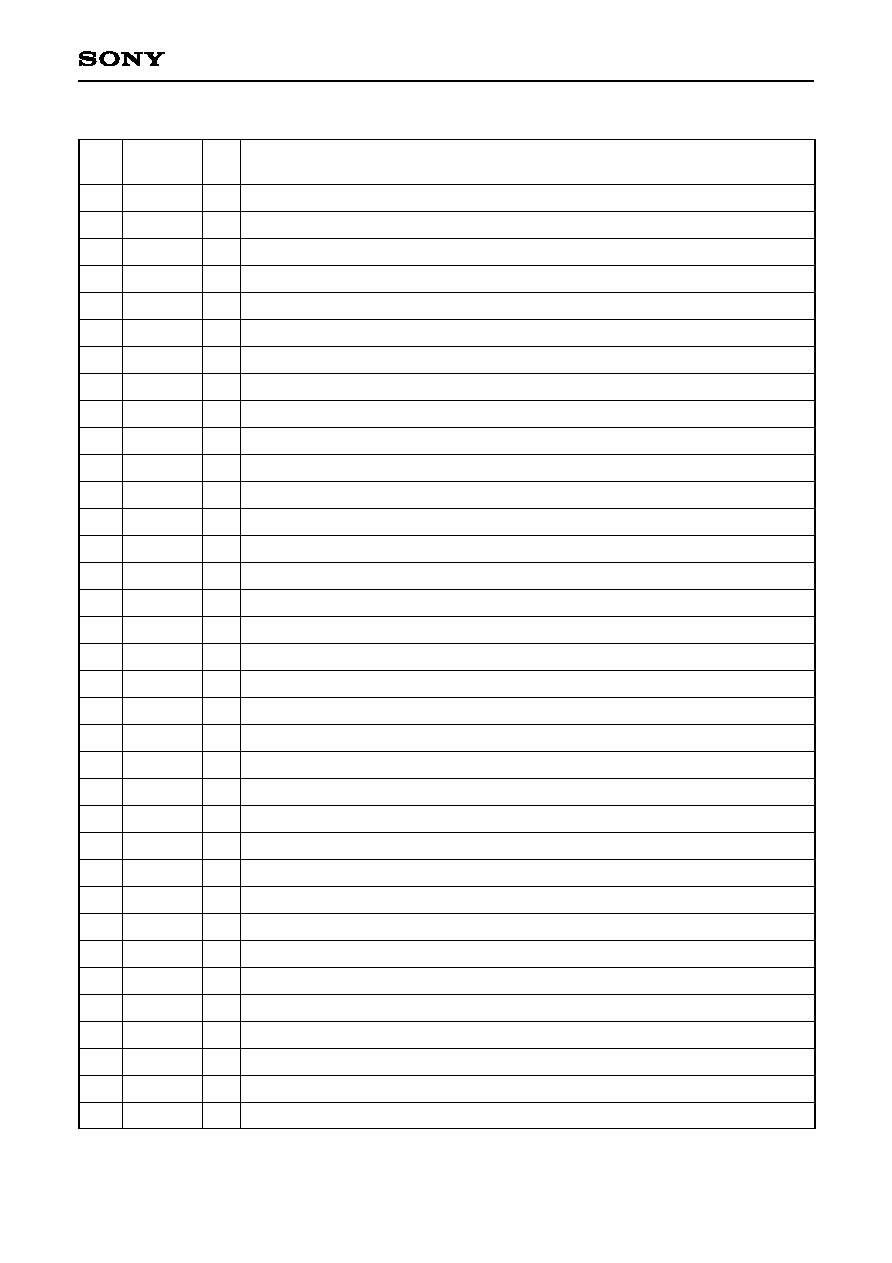

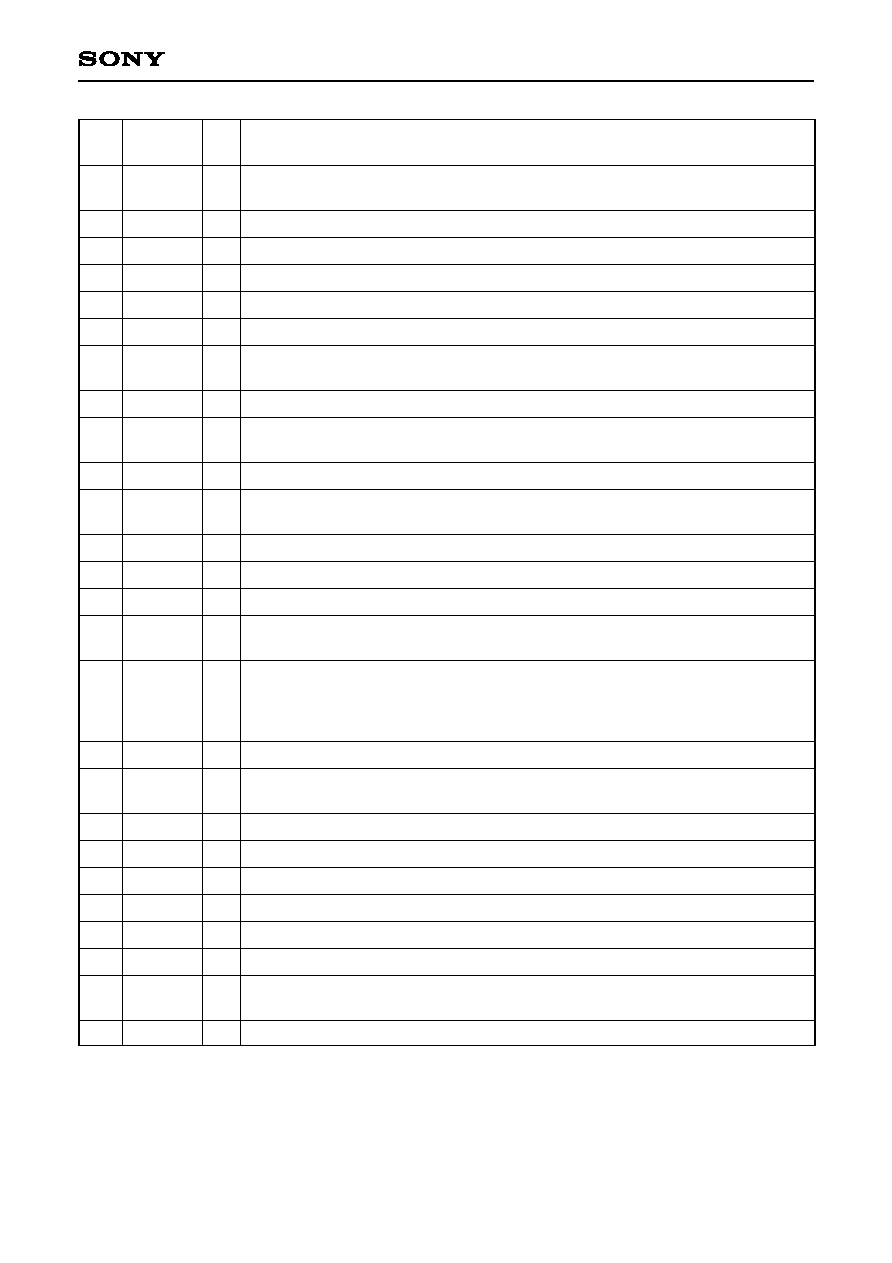

Pin Description

No connected.

No connected.

CCD signal processor block serial interface clock input. (Schmitt trigger)

CCD signal processor block serial interface data input. (Schmitt trigger)

CCD signal processor block test input 3. Connect to DV

SS

.

CCD signal processor block analog GND.

Capacitor connection.

CCD signal processor block analog GND.

CCD signal processor block analog power supply.

ADC output.

ADC output.

ADC output (LSB).

CCD signal processor block serial interface enable input. (Schmitt trigger)

CCD signal processor block test input 5. Connect to DV

DD

.

CCD signal processor block analog power supply.

Capacitor connection.

CCD signal processor block analog power supply.

CCD signal processor block analog GND.

ADC output.

ADC output.

ADC output.

CCD signal processor block test input 4. Connect to DV

SS

.

CCD signal processor block analog GND.

Capacitor connection.

Capacitor connection.

Capacitor connection.

CCD output signal input.

ADC output.

ADC output.

ADC output.

Capacitor connection.

Capacitor connection.

CCD signal processor block analog GND.

ADC output (MSB).

CCD signal processor block digital power supply. (Power supply for ADC)

A1

A2

A3

A4

A5

A6

A7

A8

A9

B1

B2

B3

B4

B5

B6

B7

B8

B9

C1

C2

C3

C4

C5

C6

C7

C8

C9

D1

D2

D3

D7

D8

D9

E1

E2

NC

NC

SCK2

SSI2

TEST3

AV

SS4

C8

AV

SS6

AV

DD5

D2

D1

D0

SEN2

TEST5

AV

DD4

C7

AV

DD3

AV

SS3

D5

D4

D3

TEST4

AV

SS5

C9

C3

C4

CCDIN

D8

D7

D6

C1

C2

AV

SS1

D9

DV

DD1

--

--

I

I

I

--

--

--

--

O

O

O

I

I

--

--

--

--

O

O

O

I

--

--

--

--

I

O

O

O

--

--

--

O

--

Pin

No.

Symbol

I/O

Description

≠ 5 ≠

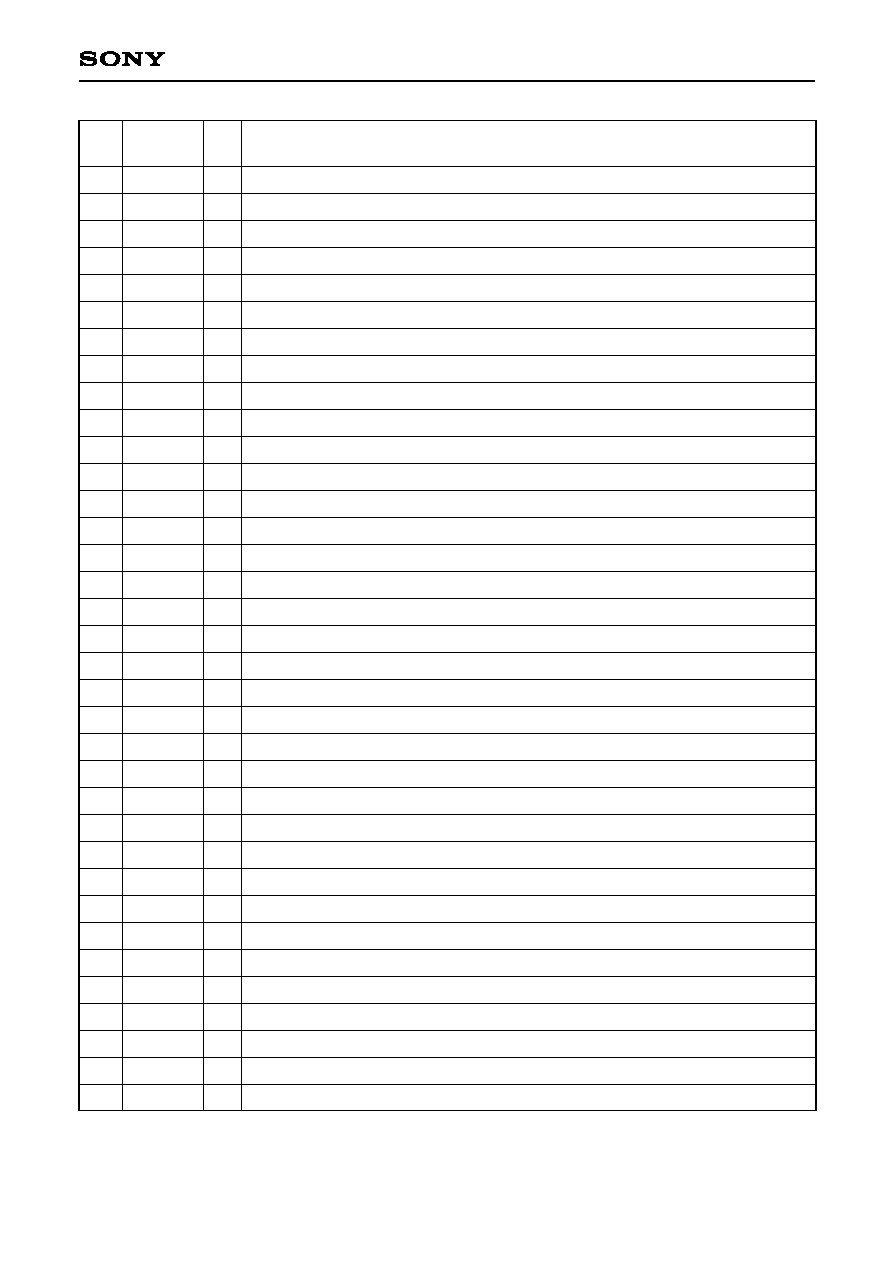

CXD3406GA

CCD signal processor block digital GND. (GND for ADC)

CCD signal processor block analog GND.

CCD signal processor block analog power supply.

CCD signal processor block analog power supply.

CCD signal processor block digital GND.

CCD signal processor block digital GND.

CCD signal processor block digital power supply.

Pulse input for horizontal and vertical blanking period pulse cleaning. (Schmitt trigger)

CCD data level sample-and-hold pulse input. (Schmitt trigger)

CCD precharge level sample-and-hold pulse input. (Schmitt trigger)

Clock input for analog/digital conversion. (Schmitt trigger)

CCD optical black signal clamp pulse input. (Schmitt trigger)

CCD dummy signal clamp pulse input. (Schmitt trigger)

Pulse output for horizontal and vertical blanking period pulse cleaning.

CCD data level sample-and-hold pulse output.

CCD precharge level sample-and-hold pulse output.

Clock output for analog/digital conversion.

CCD optical black signal clamp pulse output.

CCD dummy signal clamp pulse output.

Sample-and-hold pulse output for analog/digital conversion phase alignment.

Timing generator block digital power supply. (Power supply for CDS block)

Timing generator block 3.0 to 5.0V power supply. (Power supply for H1/H2)

Inverter input.

Inverter output.

Timing generator block digital GND.

Timing generator block digital GND.

CCD horizontal register clock output.

CCD horizontal register clock output.

Inverter output for oscillation. When not used, leave open or connect a capacitor.

System clock output for signal processor IC.

Timing generator block digital power supply. (Power supply for common logic block)

Timing generator block digital power supply. (Power supply for RG)

CCD reset gate pulse output.

Timing generator block digital GND.

Inverter input for oscillation. When not used, fix to low.

E3

E7

E8

E9

F1

F2

F3

F7

F8

F9

G1

G2

G3

G7

G8

G9

H1

H2

H3

H7

H8

H9

J1

J2

J3

J7

J8

J9

K1

K2

K3

K7

K8

K9

L1

DV

SS1

AV

SS2

AV

DD2

AV

DD1

DV

SS2

DV

SS3

DV

DD2

PBLKI

XSHDI

XSHPI

ADCLKI

CLPOBI

CLPDMI

PBLK

XSHD

XSHP

ADCLK

CLPOB

CLPDM

XRS

V

DD4

V

DD3

CKI

CKO

V

SS5

V

SS3

H1

H2

OSCO

MCKO

V

DD5

V

DD2

RG

V

SS2

OSCI

--

--

--

--

--

--

--

I

I

I

I

I

I

O

O

O

O

O

O

O

--

--

I

O

--

--

O

O

O

O

--

--

O

--

I

Pin

No.

Symbol

I/O

Description

≠ 6 ≠

CXD3406GA

Timing generator block serial interface data input.

Schmitt trigger input/No protective diode on power supply side.

Timing generator block digital GND.

Timing generator block digital GND. (GND for vertical driver)

CCD vertical register clock output.

CCD vertical register clock output.

Timing generator block digital GND.

Internal SSG enable.

High: Internal SSG valid, Low: External SYNC valid

(With pull-down resistor)

Timing generator block digital power supply.(Power supply for common logic block)

Timing generator block serial interface clock input.

Schmitt trigger input/No protective diode on power supply side.

Vertical sync signal input/output.

Timing generator block test input 1.

Normally fix to GND.

(With pull-down resistor)

CCD vertical register clock output.

Timing generator block 15.0V power supply. (Power supply for vertical driver)

Timing generator block ≠7.5V power supply. (Power supply for vertical driver)

Timing generator block test input 2.

Normally fix to GND.

(With pull-down resistor)

Timing generator block reset input.

High: Normal operation, Low: Reset control

Normally apply reset during power-on.

Schmitt trigger input/No protective diode on power supply side

Memory write timing pulse output.

Timing generator block serial interface strobe input.

Schmitt trigger input/No protective diode on power supply side

Horizontal sync signal input/output.

Timing generator block digital GND.

CCD vertical register clock output.

CCD vertical register clock output.

CCD vertical register clock output.

CCD electronic shutter pulse output.

Control input used to switch sync system.

High: CKI sync, Low: MCKO sync

(With pull-down resistor)

Vertical direction line identification pulse output.

L2

L3

L4

L5

L6

L7

L8

L9

M1

M2

M3

M4

M5

M6

M7

M8

M9

N1

N2

N3

N4

N5

N6

N7

N8

N9

SSI1

V

SS4

VM

V1A

V3A

V

SS1

SSGSL

V

DD1

SCK1

VD

TEST1

V2

VH

VL

TEST2

RST

WEN

SEN1

HD

V

SS6

V4

V1B

V3B

SUB

SNCSL

ID

I

--

--

O

O

--

I

--

I

I/O

I

O

--

--

I

I

O

I

I/O

--

O

O

O

O

I

O

Pin

No.

Symbol

I/O

Description

≠ 7 ≠

CXD3406GA

Electrical Characteristics

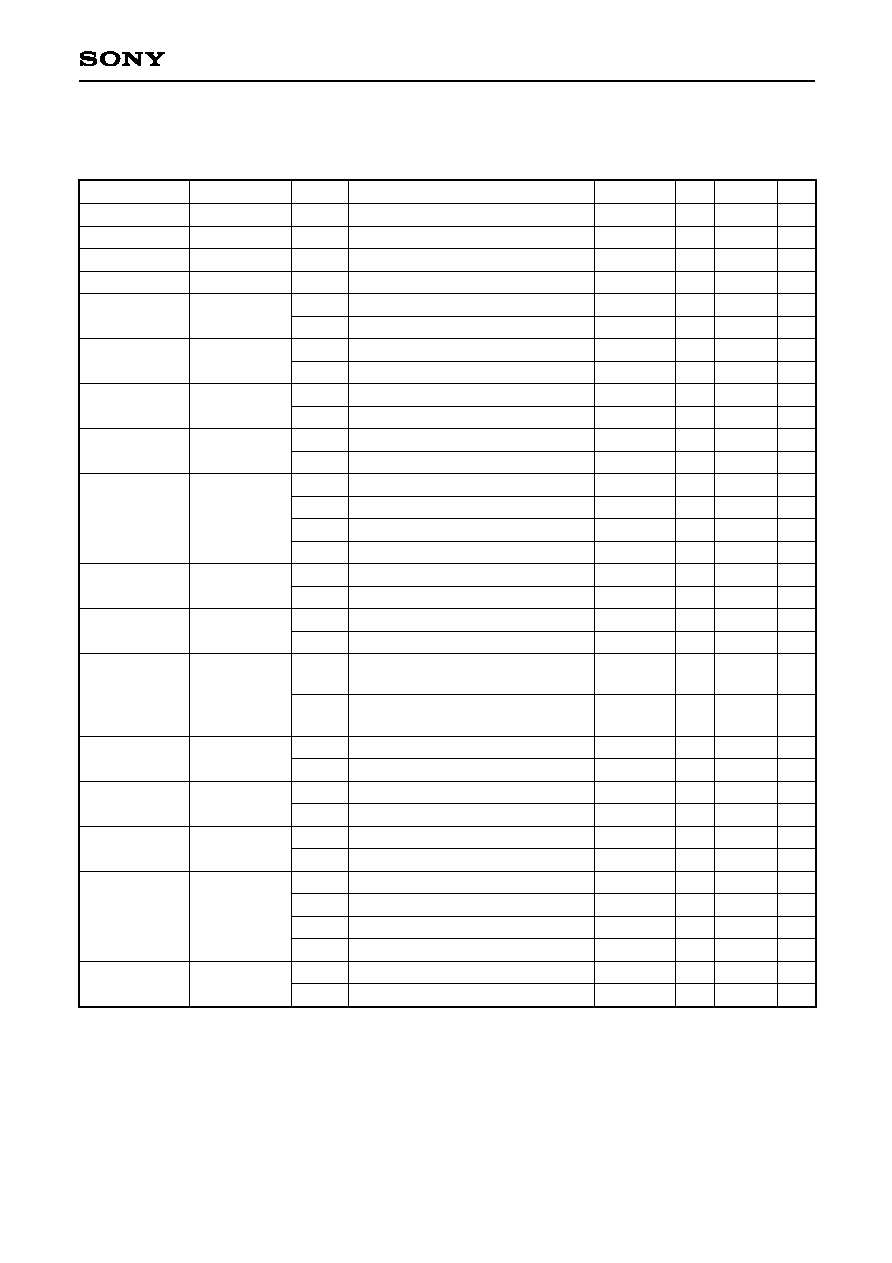

Timing Generator Block Electrical Characteristics

DC Characteristics

(Within the recommended operating conditions)

V

DD2

V

DD3

V

DD4

V

DD1

, V

DD5

RST

SSI1, SCK1,

SEN1

TEST1,

TEST2

SNCSL,

SSGSL

VD, HD

H1, H2

RG

XSHP, XSHD,

XRS, PBLK,

CLPOB,

CLPDM,

ADCLK

CKO

MCKO

ID, WEN

V1A, V1B,

V3A, V3B,

V2, V4

SUB

V

DD

a

V

DD

b

V

DD

c

V

DD

d

V

i +

V

i ≠

V

i +

V

i ≠

V

IH1

V

IL1

V

IH2

V

IL2

V

IH3

V

IL3

V

OH1

V

OL1

V

OH2

V

OL2

V

OH3

V

OL3

V

OH5

V

OL5

V

OH6

V

OL6

V

OH7

V

OL7

I

OL

I

OM1

I

OM2

I

OH

I

OSL

I

OSH

3.0

3.0

3.0

3.0

0.8V

DD

d

0.8V

DD

d

0.7V

DD

d

0.7V

DD

d

0.8V

DD

d

V

DD

d ≠ 0.8

V

DD

b ≠ 0.8

V

DD

a ≠ 0.8

V

DD

d ≠ 0.8

V

DD

d ≠ 0.8

V

DD

d ≠ 0.8

10.0

5.0

5.4

3.3

3.3

3.3

3.3

3.6

5.5

3.6

3.6

0.2V

DD

d

0.2V

DD

d

0.2V

DD

d

0.3V

DD

d

0.2V

DD

d

0.4

0.4

0.4

0.4

0.4

0.4

≠5.0

≠7.2

≠4.0

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

V

mA

mA

mA

mA

mA

mA

Feed current where I

OH

= ≠1.2mA

Pull-in current where I

OL

= 2.4mA

Feed current where I

OH

= ≠22.0mA

Pull-in current where I

OL

= 14.4mA

Feed current where I

OH

= ≠3.3mA

Pull-in current where I

OL

= 2.4mA

Feed current where I

OH

= ≠6.9mA

Pull-in current where I

OL

= 4.8mA

Feed current where I

OH

= ≠3.3mA

Pull-in current where I

OL

= 2.4mA

Feed current where I

OH

= ≠2.4mA

Pull-in current where I

OL

= 4.8mA

V1A/B, V2, V3A/B, V4 = ≠8.25V

V1A/B, V2, V3A/B, V4 = ≠0.25V

V1A/B, V3A/B = 0.25V

V1A/B, V3A/B = 14.75V

SUB = ≠8.25V

SUB = 14.75V

Supply voltage 1

Supply voltage 2

Supply voltage 3

Supply voltage 4

Input

voltage 1

1

Input

voltage 2

2

Input

voltage 3

3

Input

voltage 4

4

Input/output

voltage

Output

voltage 1

Output

voltage 2

Output

voltage 3

Output

voltage 4

Output

voltage 5

Output

voltage 6

Output

current 1

Output

current 2

Item

Pins

Symbol

Conditions

Min.

Typ.

Max.

Unit

1

This input pin is a schmitt trigger input and it does not have protective diode of the power supply side in the IC.

2

These input pins are schmitt trigger inputs.

3

These input pins are with pull-down resistor in the IC.

4

These input pins are with pull-down resistor in the IC and they do not have protective diode of the power

supply side in the IC.

Note) The above table indicates the condition for 3.3V drive.

V

OH4

Feed current where I

OH

= ≠3.3mA

V

DD

c ≠ 0.8

V

V

OL4

Pull-in current where I

OL

= 2.4mA

0.4

V

≠ 8 ≠

CXD3406GA

Inverter I/O Characteristics for Oscillation

(Within the recommended operating conditions)

Item

Logical Vth

Input

voltage

Output

voltage

Feedback

resistor

Oscillation

frequency

Pins

OSCI

OSCI

OSCO

OSCI, OSCO

OSCI, OSCO

Symbol

LVth

V

IH

V

IL

V

OH

V

OL

RFB

f

Conditions

Feed current where I

OH

= ≠3.6mA

Pull-in current where I

OL

= 2.4mA

V

IN

= V

DD

d or V

SS

Min.

0.7V

DD

d

V

DD

d ≠ 0.8

500k

20

Typ.

V

DD

d/2

2M

Max.

0.3V

DD

d

0.4

5M

50

Unit

V

V

V

V

V

MHz

Item

Logical Vth

Input

voltage

Input

amplitude

Pins

CKI

Symbol

LVth

V

IH

V

IL

V

IN

Conditions

fmax 50MHz sine wave

Min.

0.7V

DD

d

0.3

Typ.

V

DD

d/2

Max.

0.3V

DD

d

Unit

V

V

V

Vp-p

Item

Rise time

Fall time

Output noise voltage

Symbol

TTLM

TTMH

TTLH

TTML

TTHM

TTHL

VCLH

VCLL

VCMH

VCML

Conditions

VL to VM

VM to VH

VL to VH

VM to VL

VH to VM

VH to VL

Min.

200

200

30

200

200

30

Typ.

350

350

60

350

350

60

Max.

500

500

90

500

500

90

1.0

1.0

1.0

1.0

Unit

ns

ns

ns

ns

ns

ns

V

V

V

V

Inverter Input Characteristics for Base Oscillation Clock Duty Adjustment

(Within the recommended operating conditions)

Note) Input voltage is the input voltage characteristics for direct input from an external source. Input amplitude

is the input amplitude characteristics in the case of input through a capacitor.

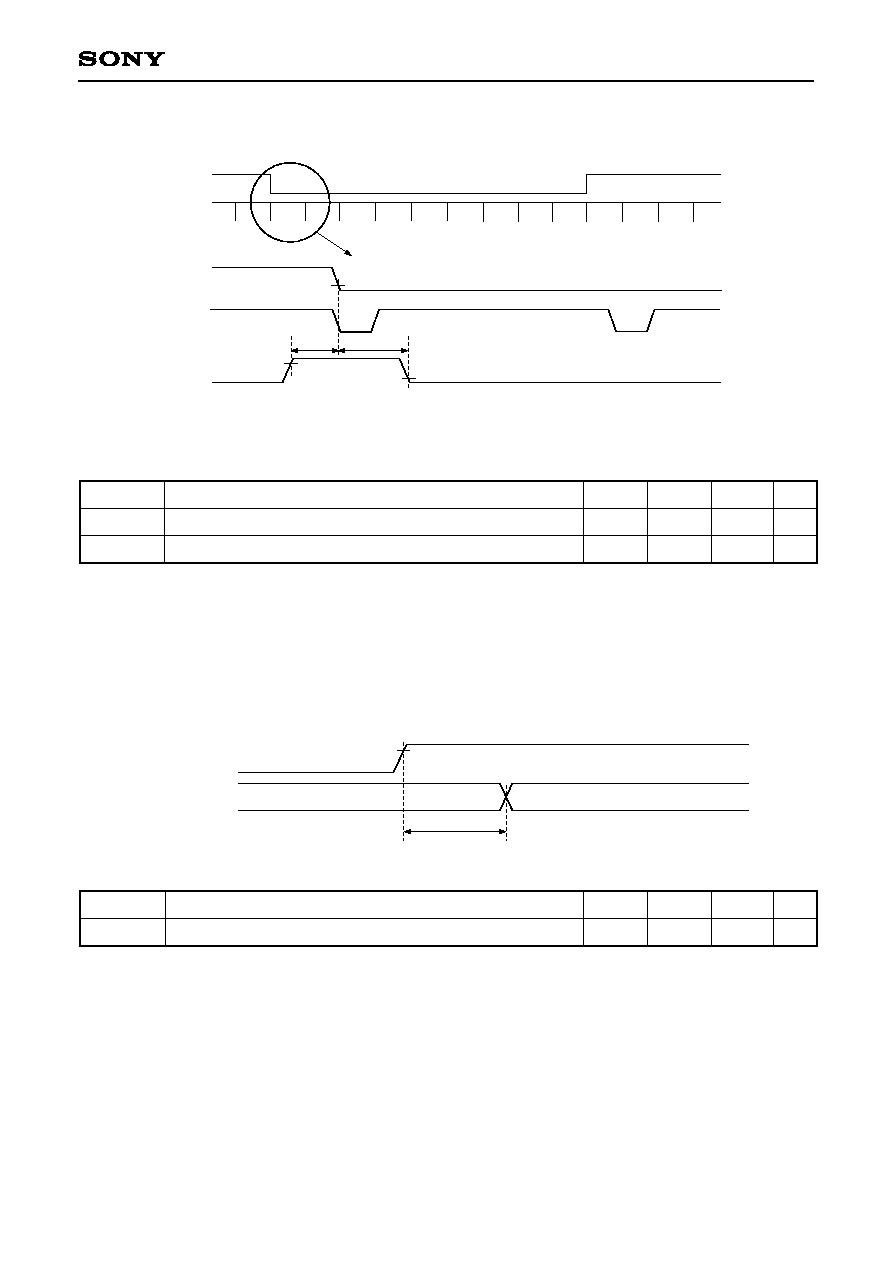

Switching Characteristics

(VH = 15.0V, VM = GND, VL = ≠7.5V)

Notes)

1. The MOS structure of this IC has a low tolerance for static electricity, so full care should be given for

measures to prevent electrostatic discharge.

2. For noise and latch-up countermeasures, be sure to connect a by-pass capacitor (0.1µF or more) between

each power supply pin (VH, VL) and GND.

3. To protect the CCD image sensor, clamp the SUB pin output at VH before input to the CCD image sensor.

≠ 9 ≠

CXD3406GA

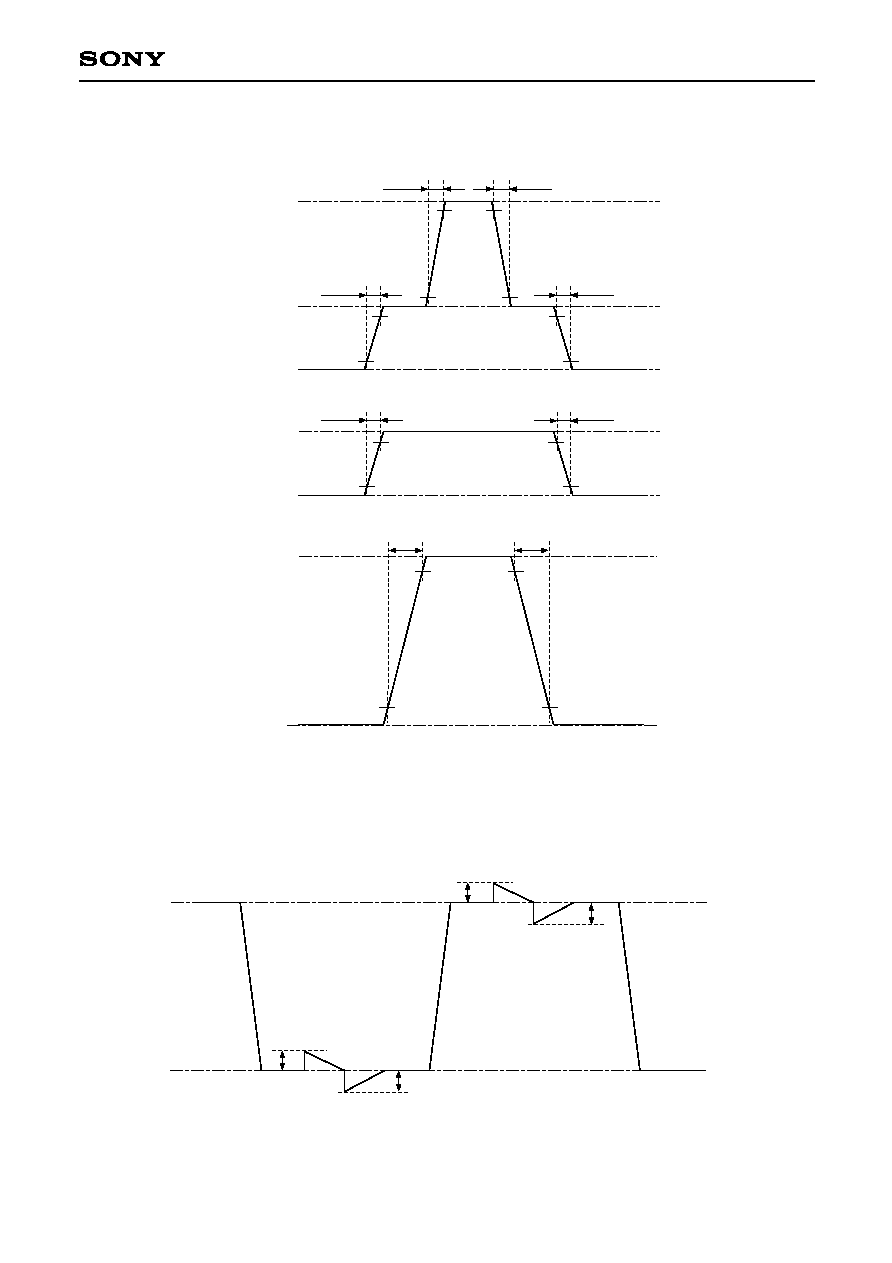

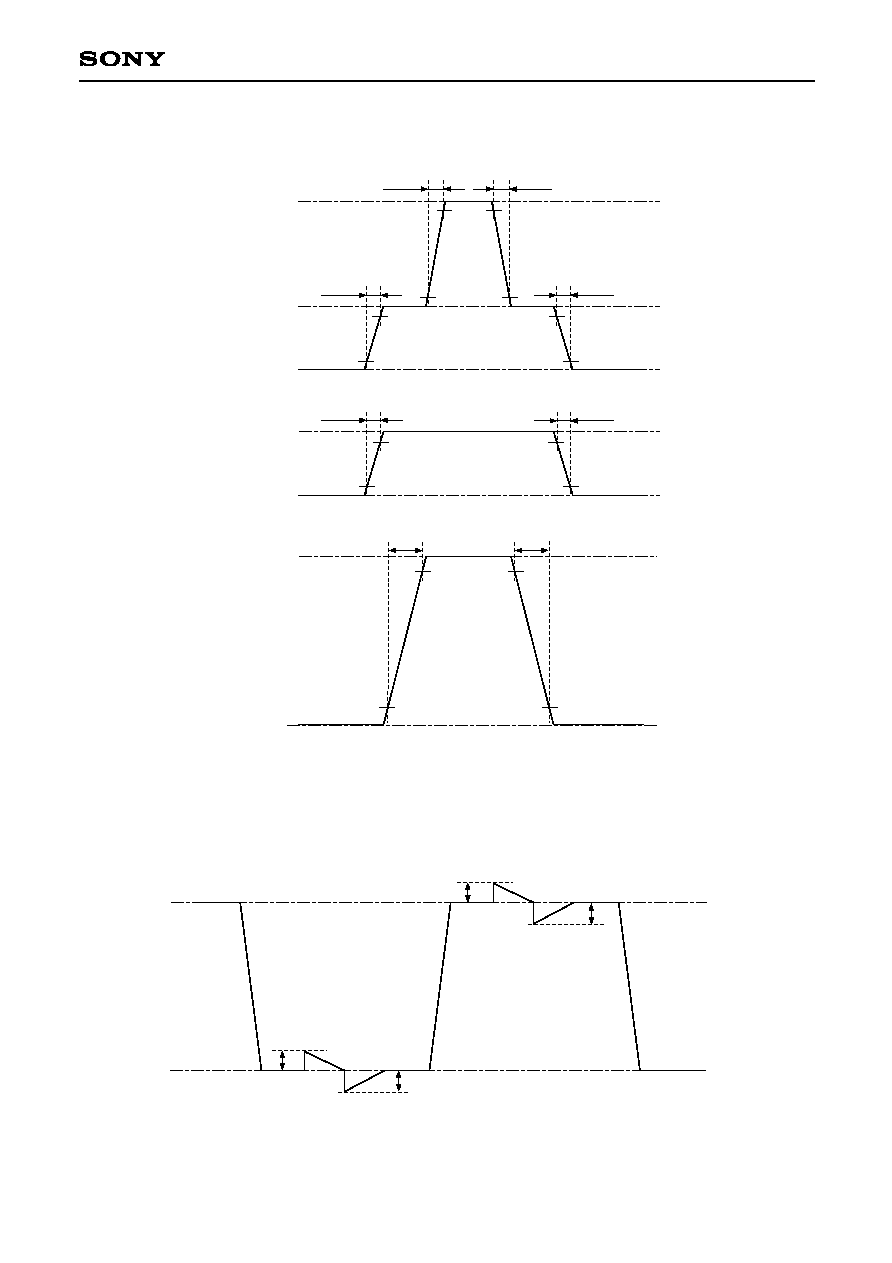

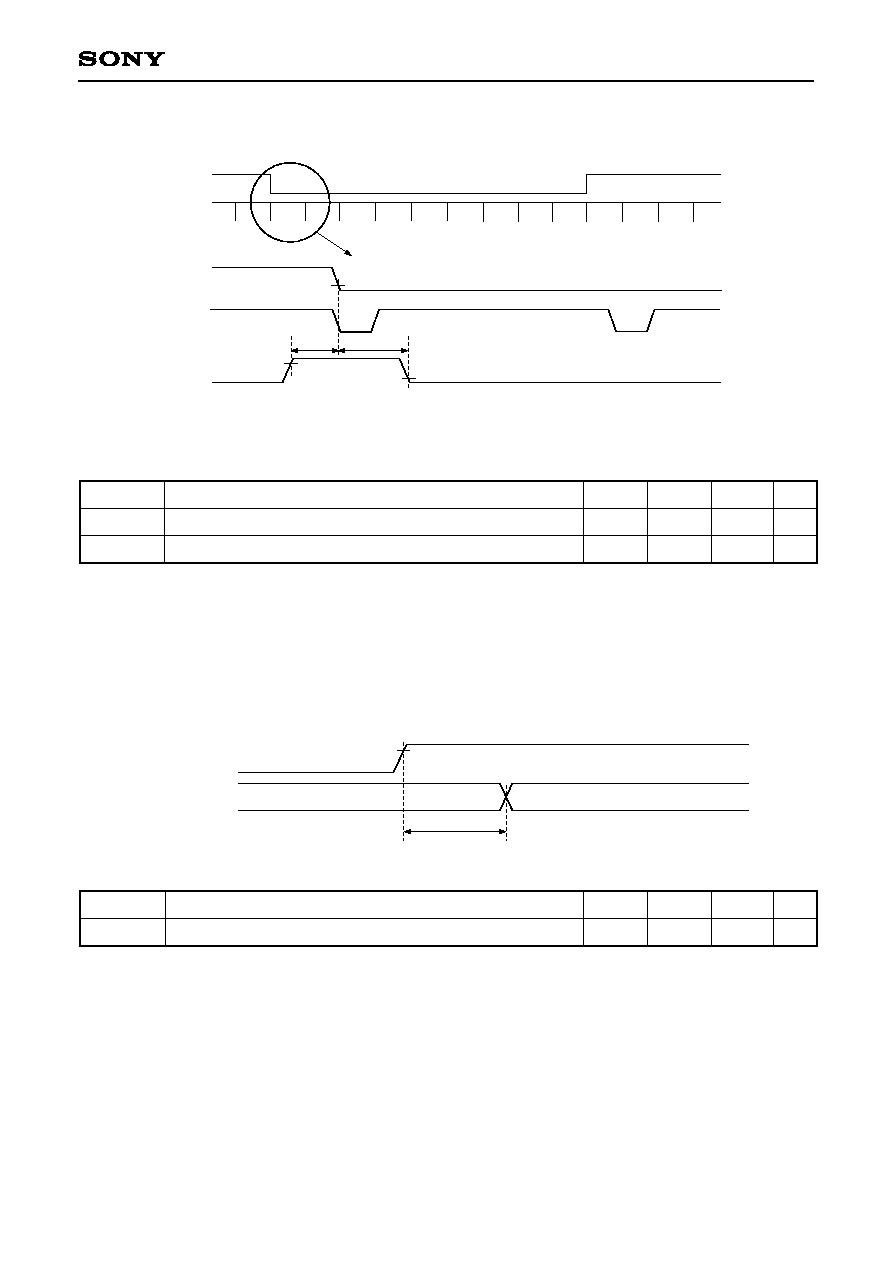

Switching Waveforms

V1A (V1B, V3A, V3B)

V2 (V4)

SUB

TTMH

TTHM

VH

VM

VL

VM

VL

VH

VL

90%

10%

90%

10%

TTLM

TTLM

90%

10%

90%

10%

TTLH

TTHL

90%

90%

10%

10%

TTML

90%

10%

TTML

90%

10%

Waveform Noise

VCMH

VCML

VM

VL

VCLH

VCLL

≠ 10 ≠

CXD3406GA

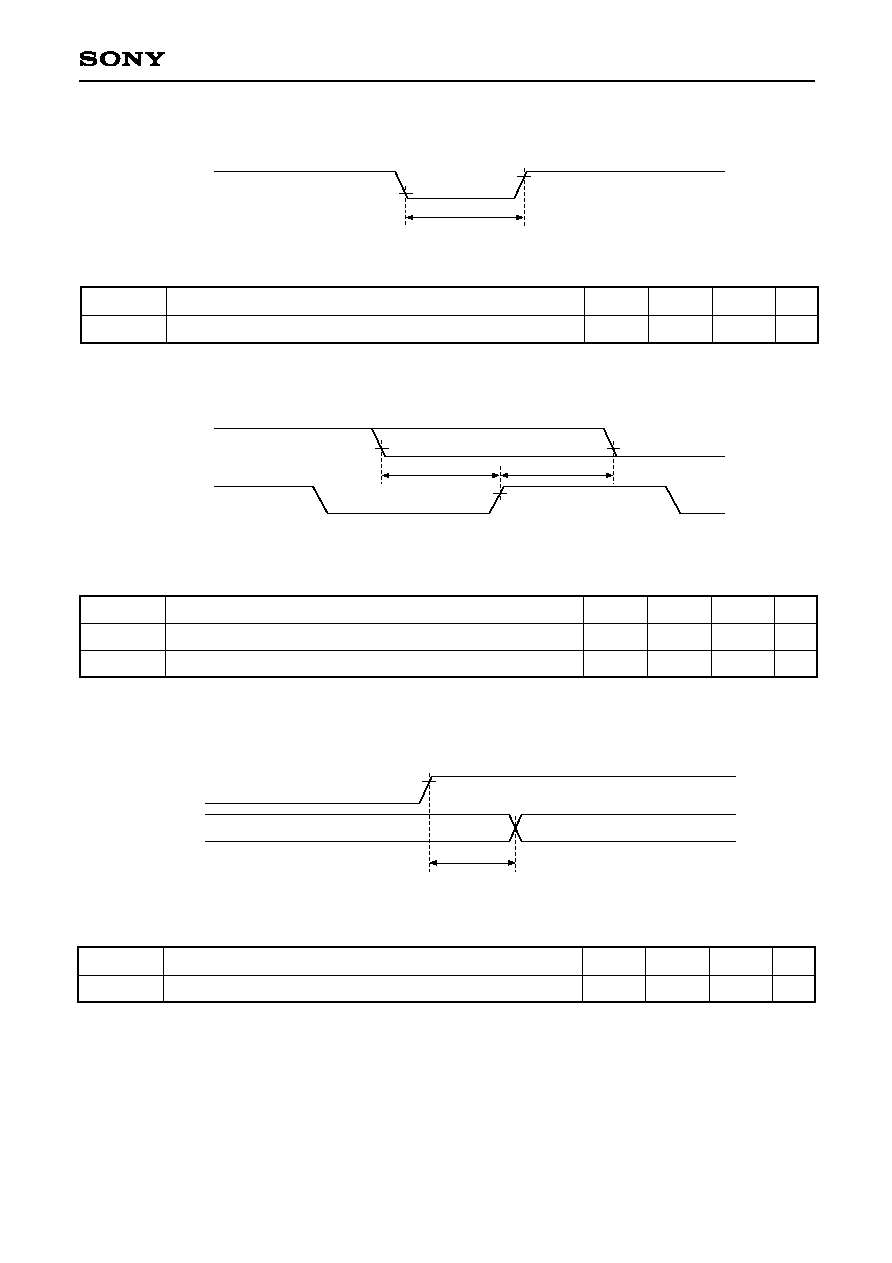

Measurement Circuit

N1

N2

L4

L5

L6

N7

L7

N8

N9

M1

M2

M3

N4

N5

N6

M4

N3

L2

K2

K9

K8

K7

K1

L1

K3

J9

J8

J7

J3

J2

J1

H9

H8

H7

H3

H2

L3

G9

G8

G7

A2

A1

A3

A4

A5

A6

A7

A8

A9

B1

B2

B3

B4

B5

B6

B7

B9

B8

C1

C2

C3

C4

C5

C6

M5

M6

E1

L8

L9

M7

M8

M9

E8

D8

D7

D3

D2

D1

C9

C8

C7

F3

F2

G1

E9

D9

E7

G3

G2

H1

F9

F8

F7

F1

E3

E2

VD

CXD3406GA

V2

VH

VL

D9

SSGSL

V

DD1

SCK1

VD

TEST1

V4

V1B

V3B

TEST2

RST

WEN

SEN1

HD

VM

V1A

V3A

SUB

V

SS1

SNCSL

ID

CLPDMI

CLPOBI

ADCLK

XSHPI

XSHDI

PBLKI

DV

DD2

DV

SS3

ADCLKI

AV

DD1

AV

SS1

AV

SS2

DV

SS2

DV

SS1

DV

DD1

AV

DD2

C2

C1

D6

D7

D8

CCDIN

C4

C3

V

SS6

SSI1

MCKO

V

SS2

RG

V

DD2

OSCO

OSCI

V

DD5

H2

H1

V

SS3

V

SS5

CKO

CKI

V

DD3

V

DD4

XRS

CLPDM

CLPOB

V

SS4

XSHP

XSHD

PBLK

NC

NC

SCK2

SSI2

TEST3

AV

SS4

C8

AV

SS6

AV

DD5

D2

D1

D0

SEN2

TEST5

AV

DD4

C7

AV

SS3

AV

DD3

D5

D4

D3

TEST4

AV

SS5

C9

Serial interface data

HD

+3.3V

+15.0V

≠

7.5V

C2

C2

C2

C2

C2

R1

R1

R1

R2

R1

R1

R1

C2

C2

C2

C2

C2

C2

C2

C2

C2

C1

C1

C1

C1

C1

C1

C2

C3

CKI

C6

C4

C5

C5

C6

C6

C1 3300pF

C2 560pF

C3 820pF

C4 30pF

C5 215pF

C6 10pF

R1 30

R2 10

≠ 11 ≠

CXD3406GA

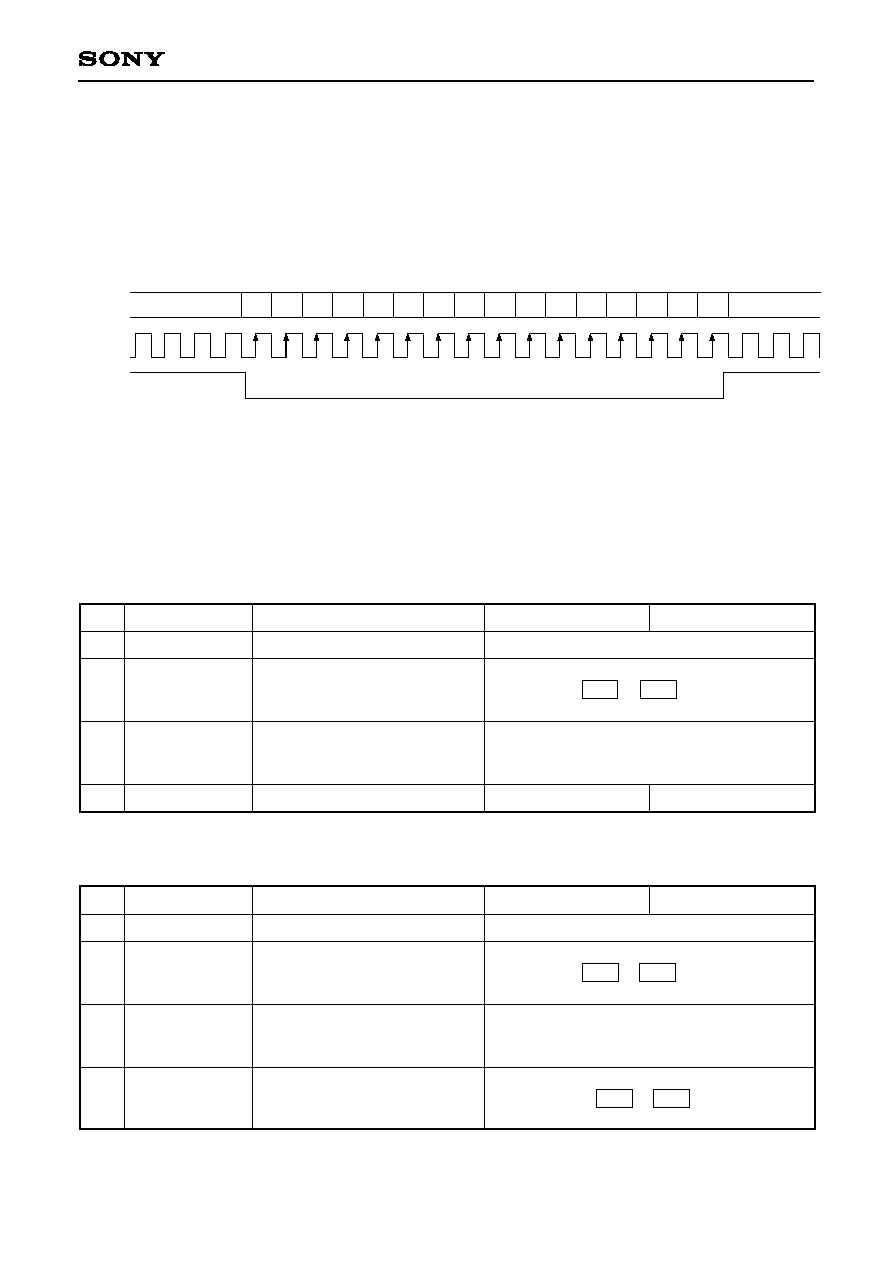

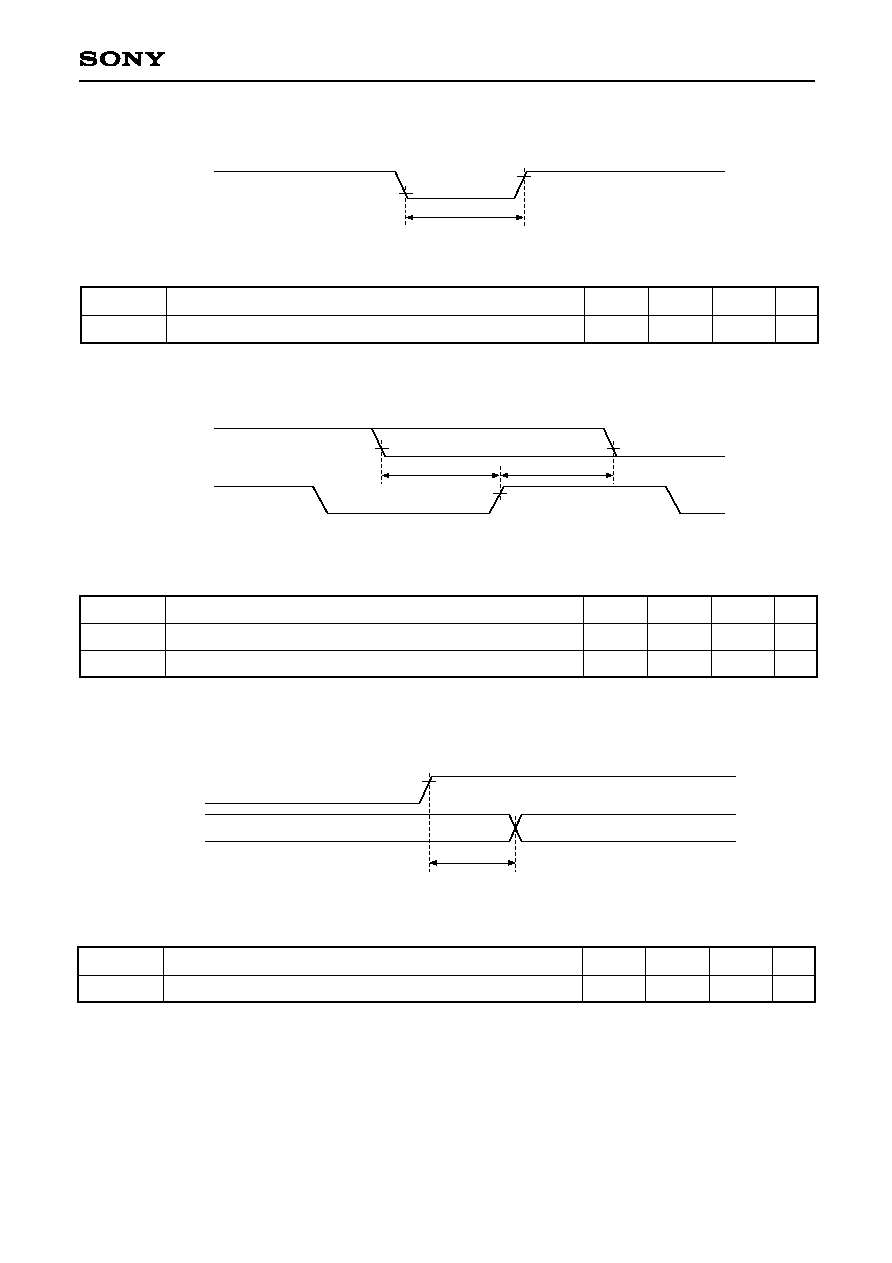

AC Characteristics

AC characteristics between the serial interface clocks

SSI1

0.2V

DD

d

0.2V

DD

d

0.8V

DD

d

ts2

th1

ts1

ts3

0.8V

DD

d

0.8V

DD

d

SCK1

SEN1

SEN1

Symbol

t

s1

t

h1

t

s2

t

s3

Definition

SSI1 setup time, activated by the rising edge of SCK1

SSI1 hold time, activated by the rising edge of SCK1

SCK1 setup time, activated by the rising edge of SEN1

SEN1 setup time, activated by the rising edge of SCK1

Min.

Typ.

Max.

20

20

20

20

Unit

ns

ns

ns

ns

Serial interface clock internal loading characteristics (1)

(Within the recommended operating conditions)

th1

Enlarged view

Example: During frame mode

0.2V

DD

d

ts1

0.2V

DD

d

V1A

VD

HD

HD

V1A

SEN1

0.8V

DD

d

Symbol

t

s1

t

h1

Definition

SEN1 setup time, activated by the falling edge of HD

SEN1 hold time, activated by the falling edge of HD

Min.

Typ.

Max.

0

102

Unit

ns

µs

Be sure to maintain a constantly high SEN1 logic level near the falling edge of the HD in the horizontal period

during which V1A/B and V3A/B values take the ternary value and during that horizontal period.

(Within the recommended operating conditions)

≠ 12 ≠

CXD3406GA

Serial interface clock output variation characteristics

Normally, the serial interface data is loaded to the CXD3406GA at the timing shown in "Serial interface clock

internal loading characteristics (1)" above. However, one exception to this is when the data such as STB is

loaded to the CXD3406GA and controlled at the rising edge of SEN1. See "Description of Operation".

0.8V

DD

d

SEN1

Output signal

tpdPULSE

Symbol

tpdPULSE

Definition

Output signal delay, activated by the rising edge of SEN1

Min.

Typ.

Max.

100

5

Unit

ns

(Within the recommended operating conditions)

Serial interface clock internal loading characteristics (2)

th1

Enlarged view

0.2V

DD

d

ts1

0.2V

DD

d

VD

HD

VD

HD

SEN1

0.8V

DD

d

Example: During frame mode

Symbol

t

s1

t

h1

Definition

SEN1 setup time, activated by the falling edge of VD

SEN1 hold time, activated by the falling edge of VD

Min.

Typ.

Max.

0

200

Unit

ns

ns

Be sure to maintain a constantly high SEN1 logic level near the falling edge of VD.

(Within the recommended operating conditions)

≠ 13 ≠

CXD3406GA

RST

0.2V

DD

d

tw1

0.8V

DD

d

VD, HD

MCKO

ts1

th1

0.2V

DD

d

0.8V

DD

d

0.2V

DD

d

RST loading characteristics

Symbol

t

w1

Definition

RST pulse width

Min.

Typ.

Max.

35

Unit

ns

(Within the recommended operating conditions)

VD and HD loading characteristics

Symbol

t

s1

t

h1

Definition

VD and HD setup time, activated by the rising edge of MCKO

VD and HD hold time, activated by the rising edge of MCKO

Min.

Typ.

Max.

20

5

Unit

ns

ns

MCKO load capacitance = 10pF

(Within the recommended operating conditions)

0.8V

DD

d

MCKO

WEN, ID

tpd1

WEN and ID load capacitance = 10pF

(Within the recommended operating conditions)

Symbol

tpd1

Definition

Time until the above outputs change after the rise of MCKO

Min.

Typ.

Max.

60

20

Unit

ns

Output variation characteristics

≠ 14 ≠

CXD3406GA

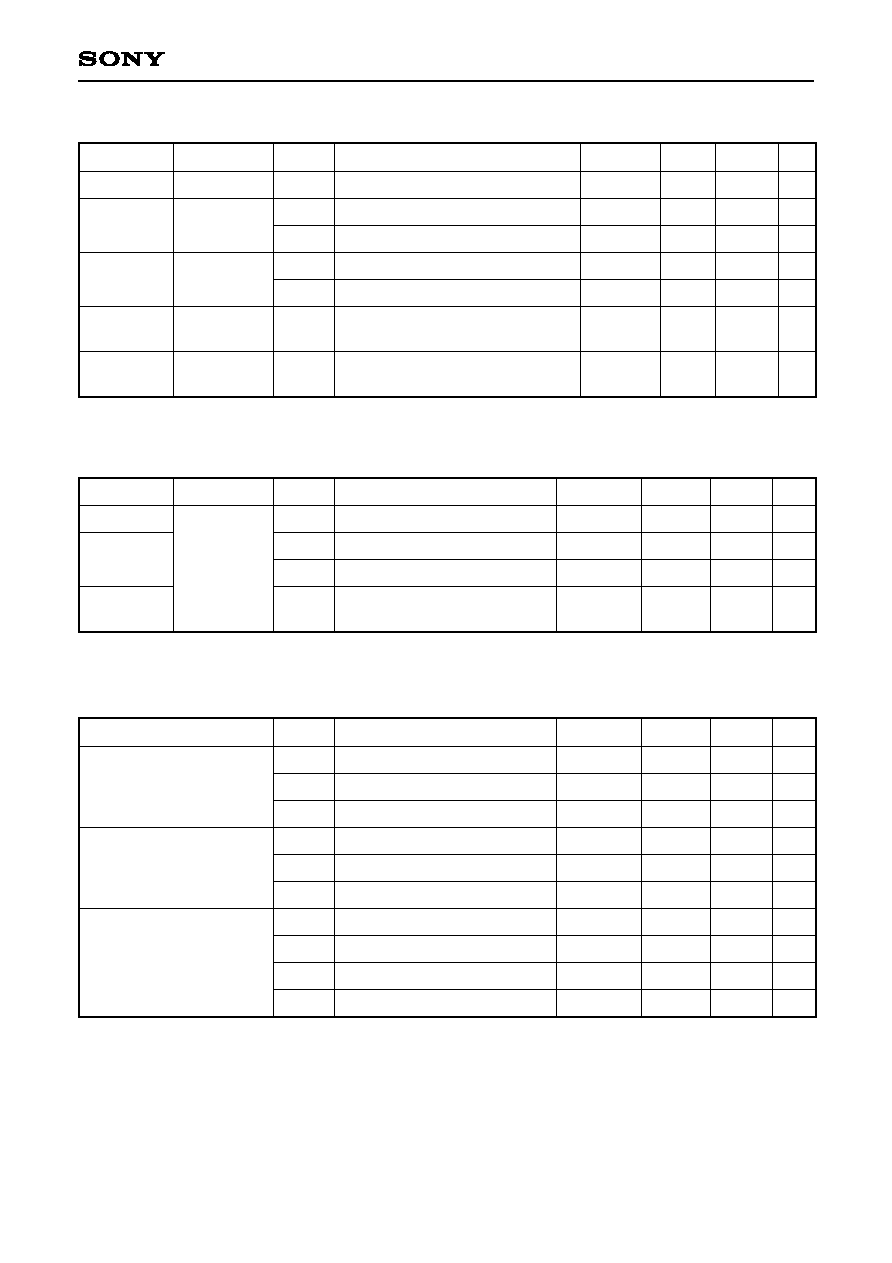

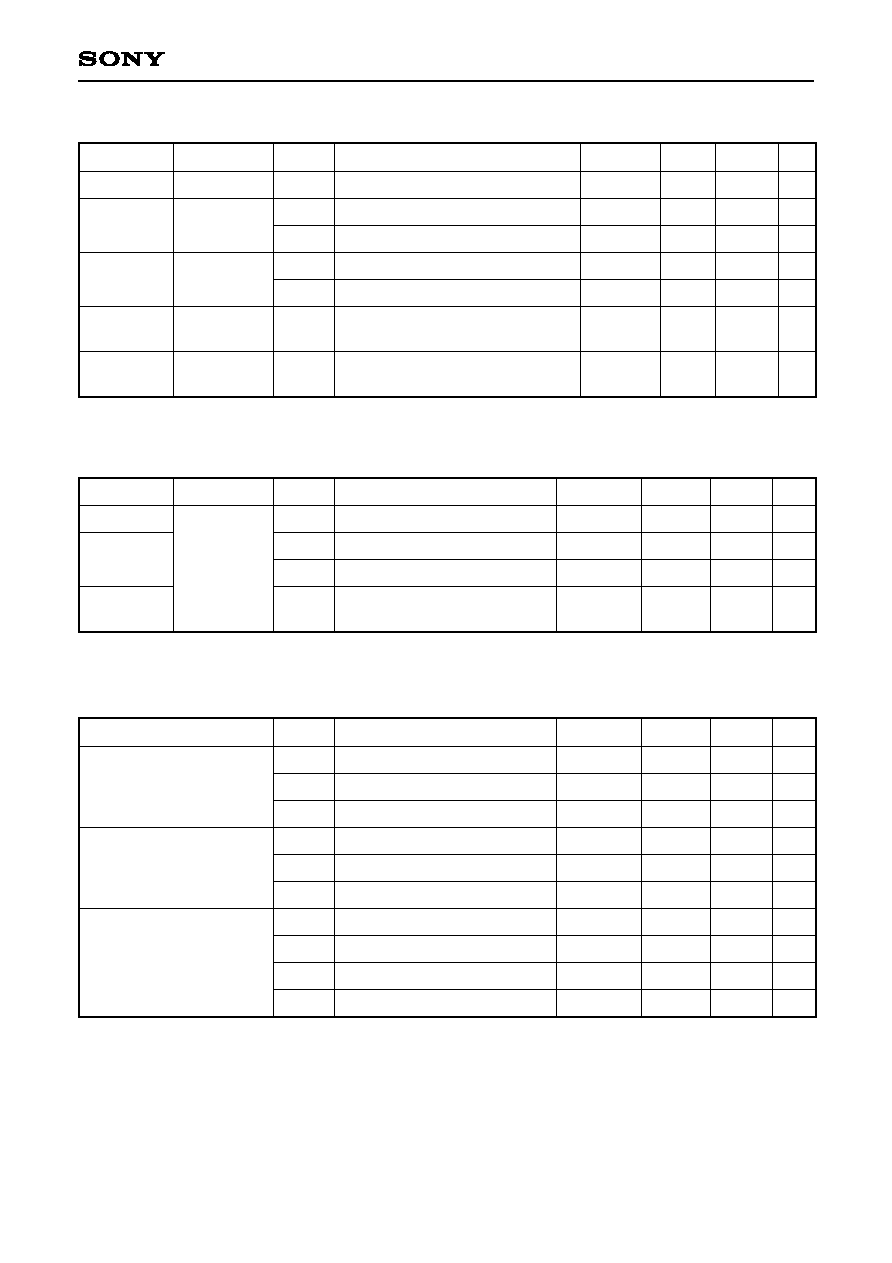

CCD Signal Processor Block Electrical Characteristics

DC Characteristics

(Fc = 18MSPS, DV

DD1

,

2

= AV

DD1

,

2

,

3

,

4

,

5

= 3.3V, Ta = 25∞C)

Item

Supply voltage 1

Supply voltage 2

Supply voltage 3

Analog input

capacitance

Input voltage

A/D clock duty

Output voltage

Pins

DV

DD1

DV

DD2

AV

DD1

,

AV

DD2

,

AV

DD3

,

AV

DD4

,

AV

DD5

CCDIN

SCK2, SSI2,

SEN2, TEST3,

TEST4, XSHDI,

XSHPI, ADCLKI,

CLPOBI,

CLPDMI, PBLKI

ADCLKI

D0 to D9

Symbol

V

DD

e

V

DD

f

V

DD

g

C

IN

V

I +

V

I ≠

V

OH

V

OL

Conditions

Feed current where I

OH

= ≠2.0mA

Pull-in current where I

OL

= 2.0mA

Min.

3.0

3.0

3.0

V

DD

e ≠ 0.9

Typ.

3.3

3.3

3.3

15

1.8

1.1

50

Max.

3.6

3.6

3.6

0.4

Unit

V

V

V

pF

V

V

%

V

V

Analog Characteristics

(Fc = 18MSPS, DV

DD1

,

2

= AV

DD1

,

2

,

3

,

4

,

5

= 3.3V, Ta = 25∞C)

Item

CCDIN input voltage amplitude

PGA maximum gain

PGA minimum gain

ADC resolution

ADC maximum conversion rate

ADC integral non-linearity error

ADC differential non-linearity error

Signal-to-noise ratio

CCDIN input voltage clamp level

CCD optical black signal clamp

level

Symbol

V

IN

Gmax

Gmin

Fc max

E

L

E

D

SNR

1

CLP

OB

Conditions

PGA gain = 0dB, output full scale

PGA gain setting data = "3FFh"

PGA gain setting data = "000h"

PGA gain = 0dB

PGA gain = 0dB

CCDIN input connected to GND

via a coupling capacitor

PGA gain = 0dB

OBLVL = "8h"

PGA gain = 0dB

Min.

900

18

Typ.

42

≠6

10

±1.0

±0.5

62

1.5

32

Max.

1100

±5.0

±1.0

Unit

mV

dB

dB

bit

MHz

LSB

LSB

dB

V

LSB

1

SNR = 20 log (full-scale voltage/rms noise)

≠ 15 ≠

CXD3406GA

AC Characteristics

AC characteristics between the serial interface clocks

SSI2

0.2V

DD

0.2V

DD

0.8V

DD

ts2

th1

ts1

ts3

0.8V

DD

0.8V

DD

SCK2

SEN2

SEN2

Symbol

t

p1

t

s1

t

h1

t

s2

t

s3

Definition

SCK2 clock period

SSI2 setup time, activated by the rise of SCK2

SSI2 hold time, activated by the rise of SCK2

SCK2 setup time, activated by the rise of SEN2

SEN2 setup time, activated by the rise of SCK2

Min.

Typ.

Max.

100

30

30

30

30

Unit

ns

ns

ns

ns

ns

(Fc = 18MSPS, DV

DD1

,

2

= AV

DD1

,

2

,

3

,

4

,

5

= 3.3V, Ta = 25∞C)

The setting values are reflected to the operation 5 or 6 ADCLKI clocks after the serial data is loaded at the

rise of SEN2.

≠ 16 ≠

CXD3406GA

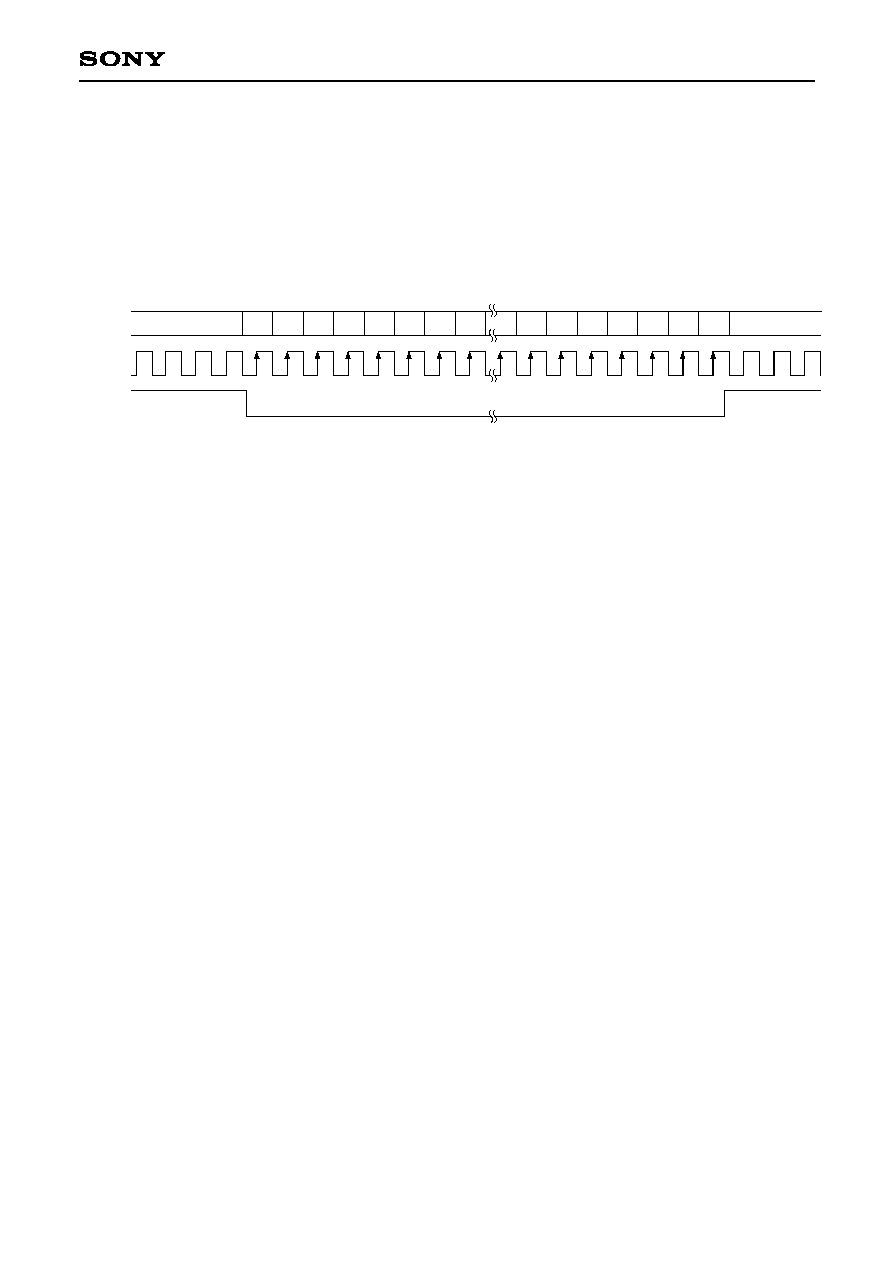

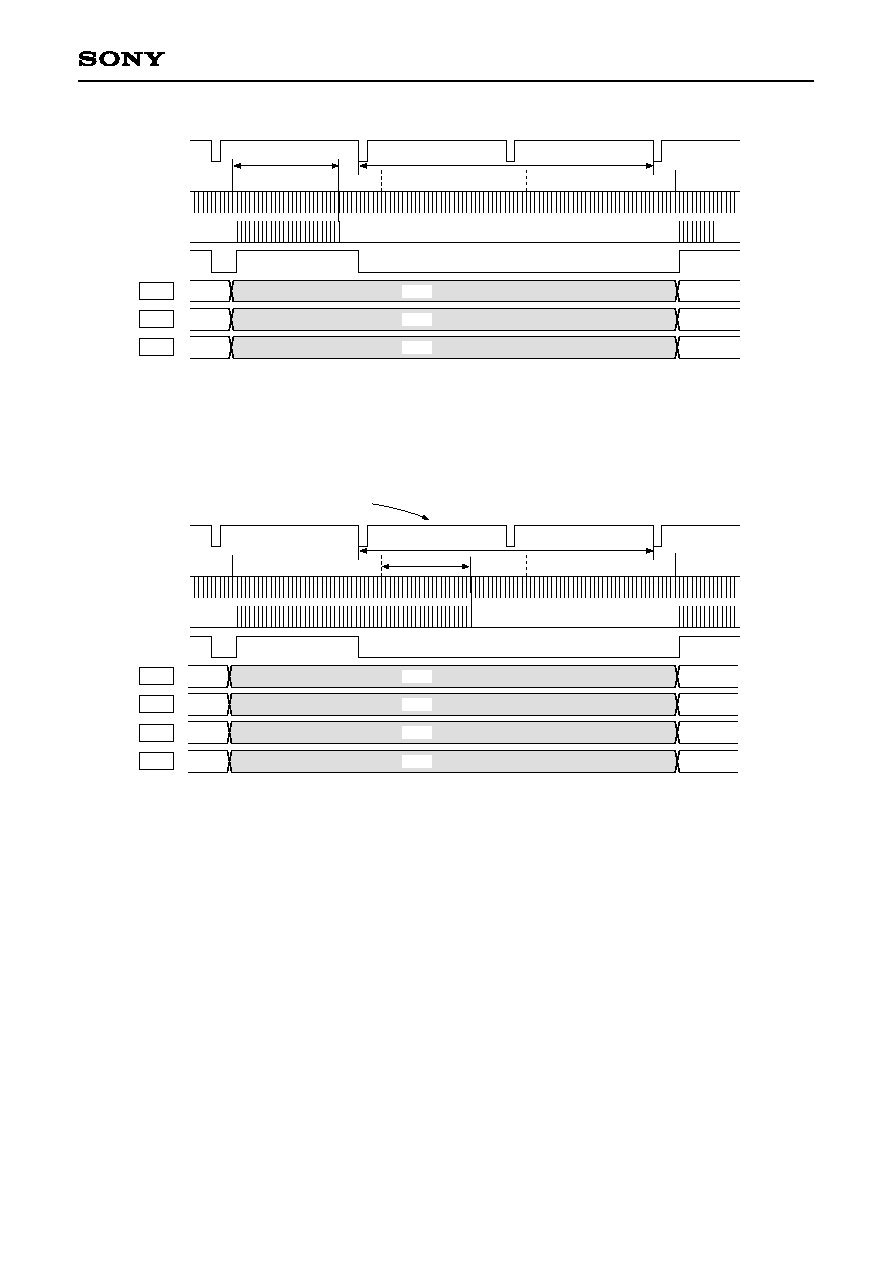

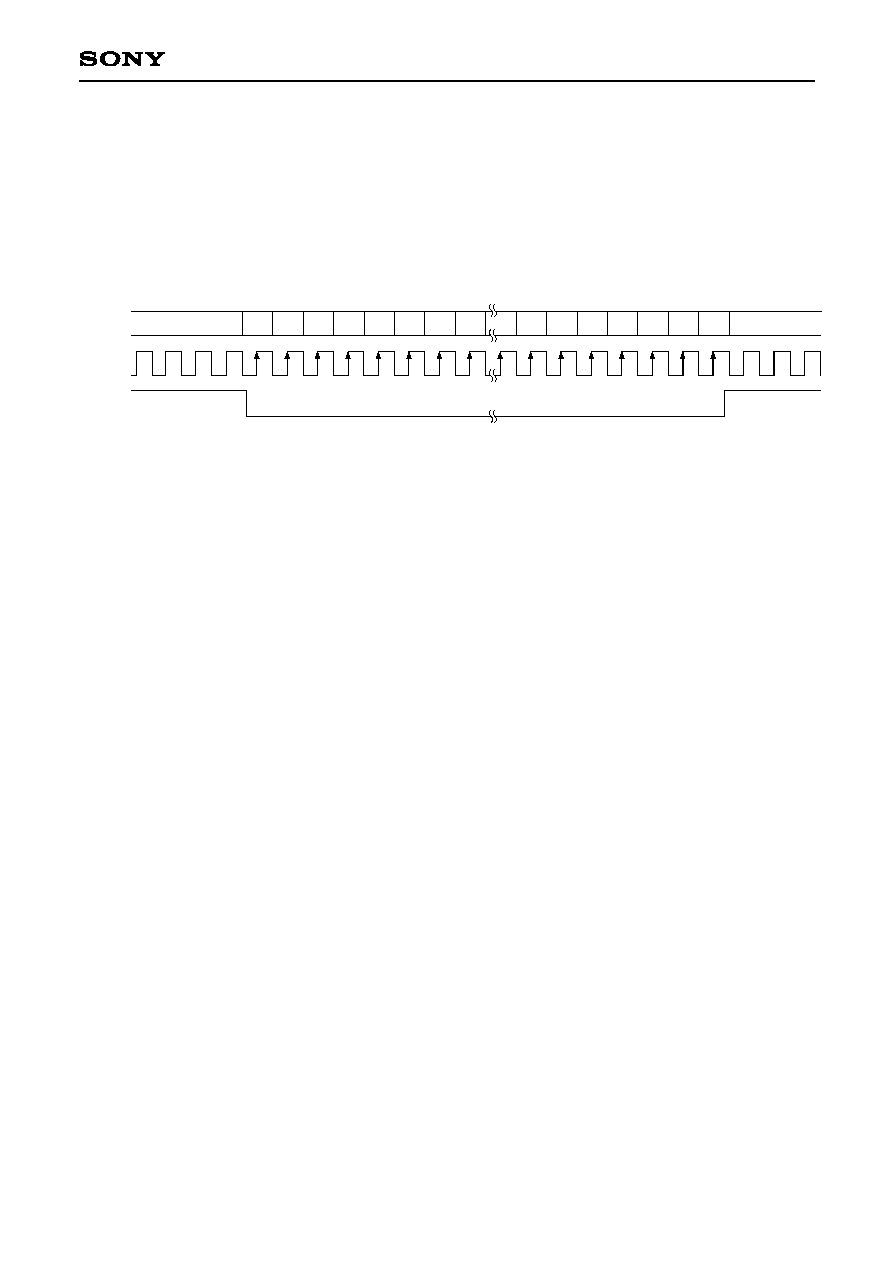

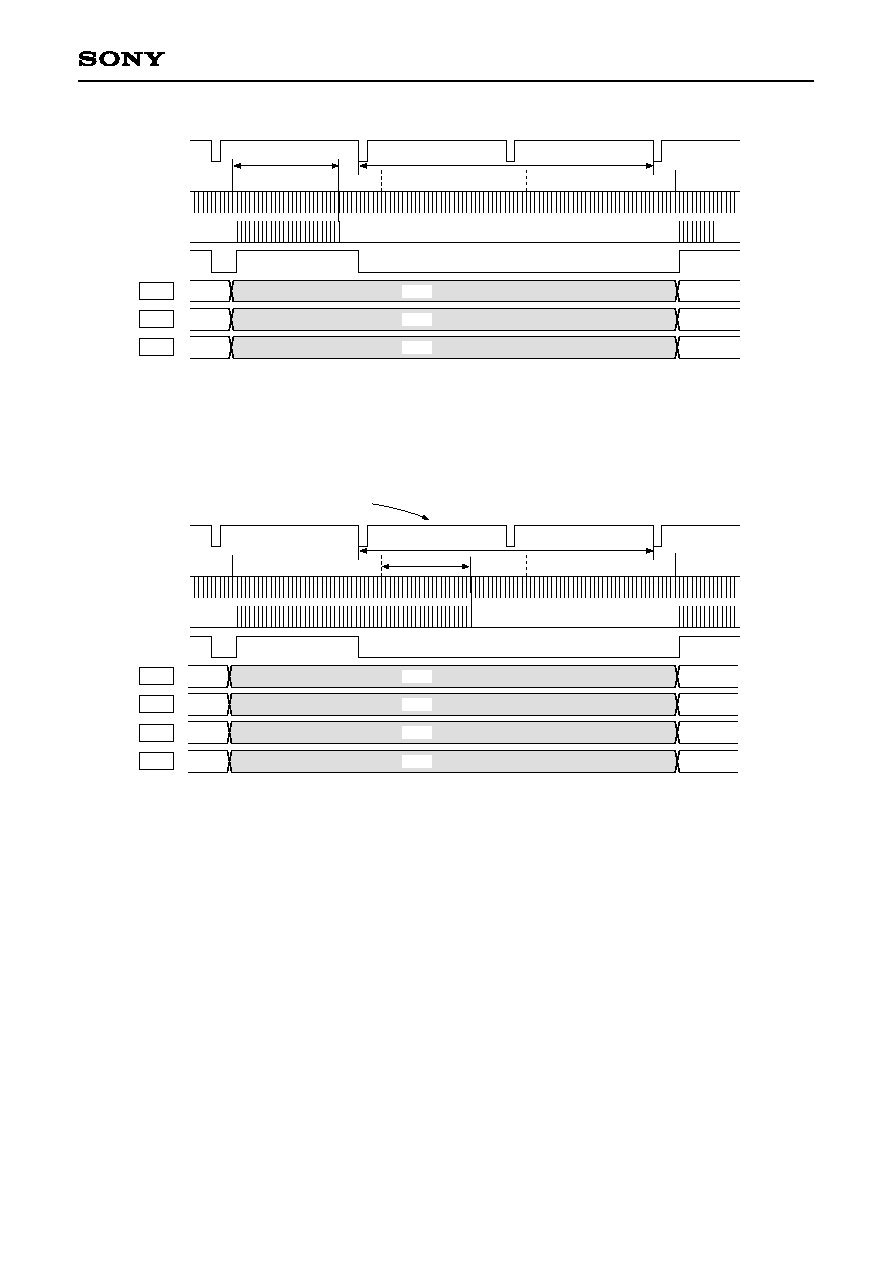

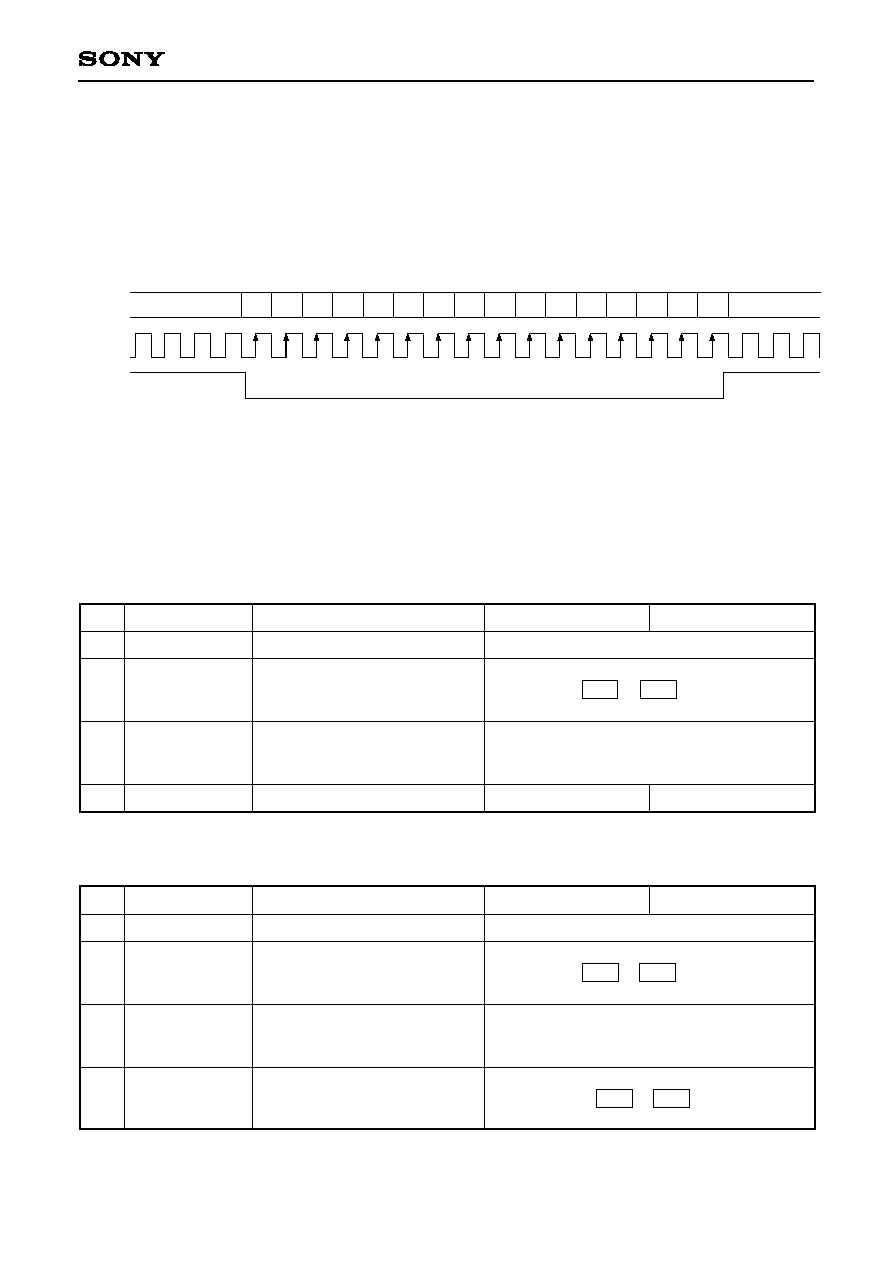

CDS/ADC Timing Chart

N

N + 1

N ≠ 10

CCDIN

XSHPI

XSHDI

ADCLKI

D0 to D9

N ≠ 9

N ≠ 8

N ≠ 7

tw1

DL

N + 2

N + 3

Symbol

t

w1

DL

Definition

ADCLKI clock period

ADCLKI clock duty

Data latency

Min.

Typ.

Max.

50

9

54

Unit

ns

%

clocks

(Fc = 18MSPS, DV

DD1

,

2

= AV

DD1

,

2

,

3

,

4

,

5

= 3.3V, Ta = 25∞C)

Set the input pulse polarity setting data D13, D14 and D15 of the serial interface data to "0".

Preblanking Timing Chart

11 Clocks

11 Clocks

PBLKI

ADCLKI

D0 to D9

All "0"

≠ 17 ≠

CXD3406GA

Description of Operation

Pulses output from the CXD3406GA's timing generator block are controlled mainly by the RST pin and by the

serial interface data. The Pin Status Table is shown below, and the details of serial interface control are

described on page 19 and thereafter.

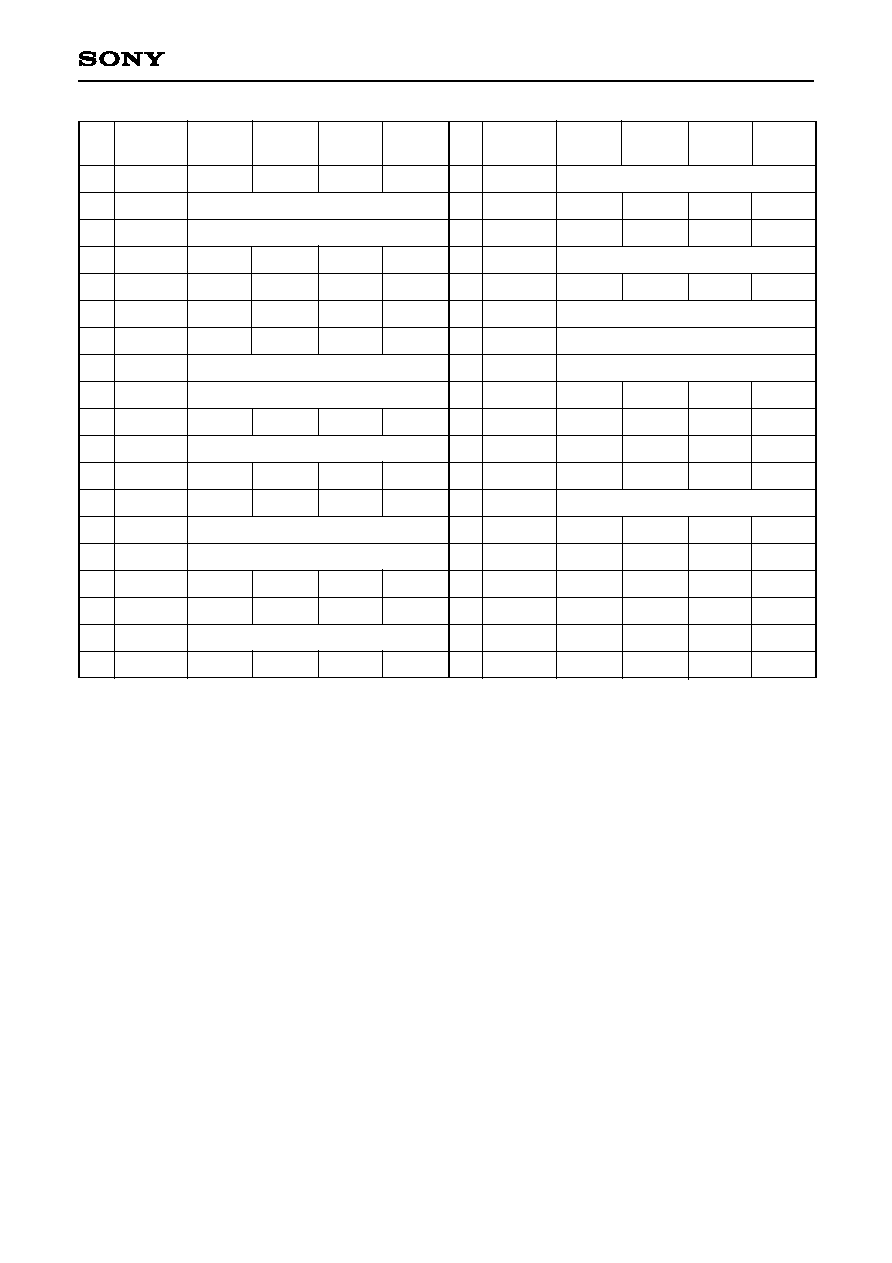

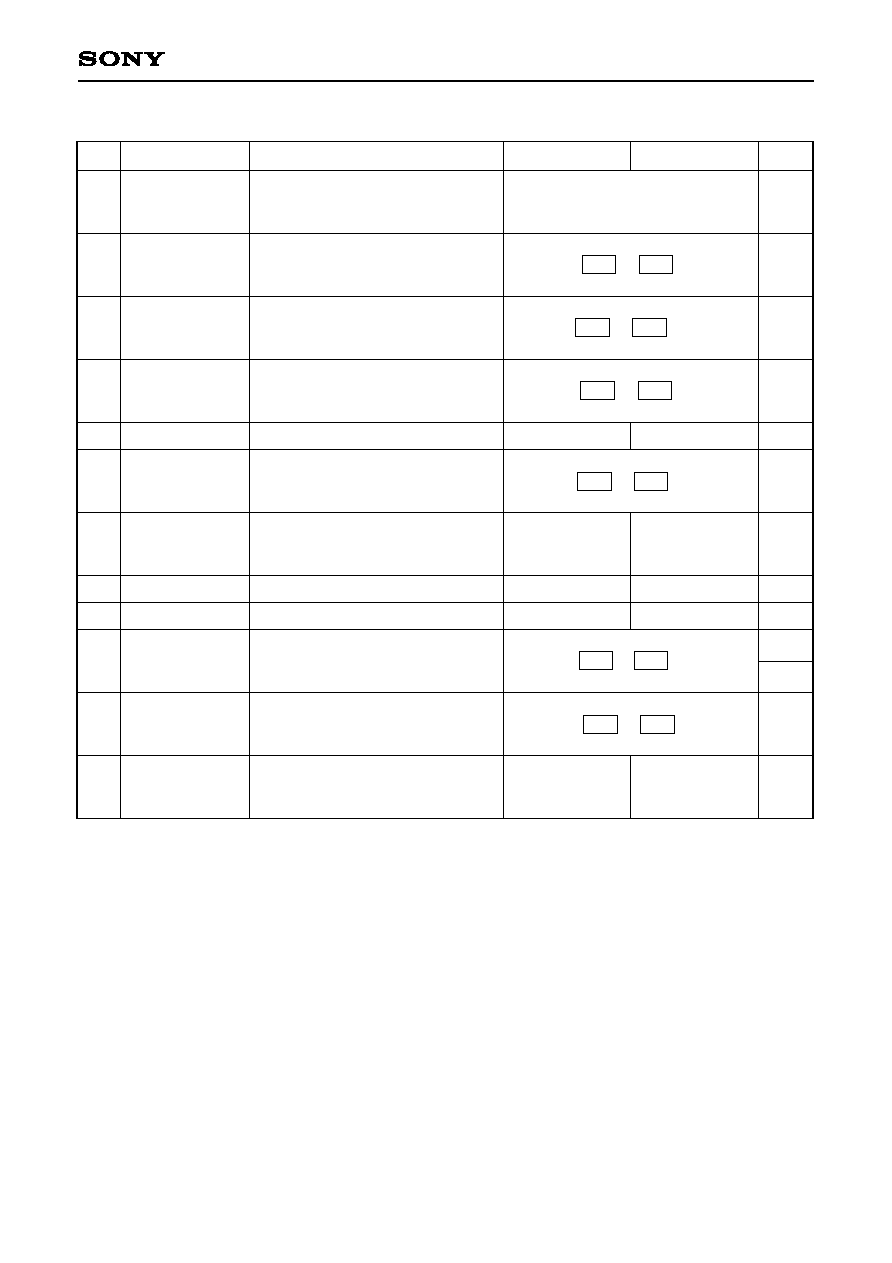

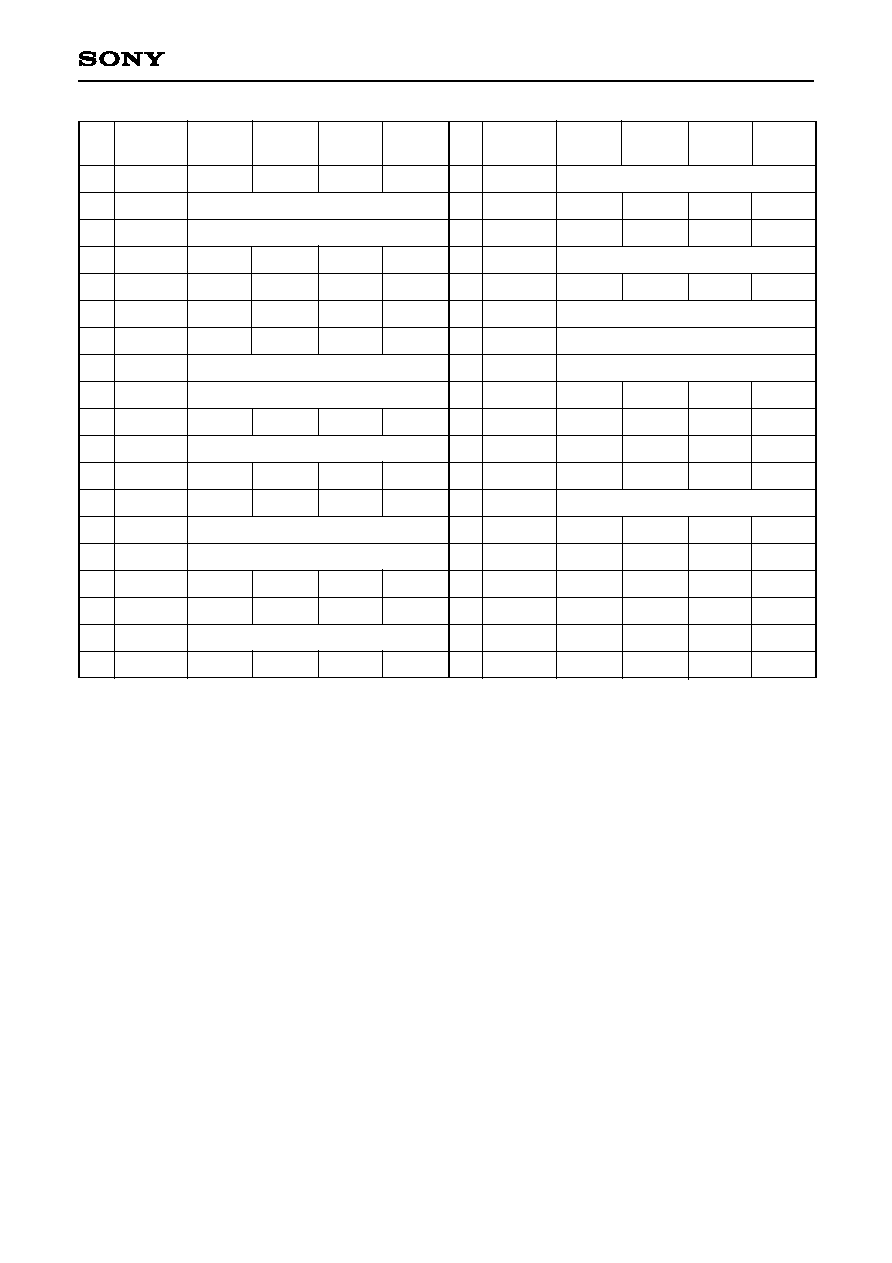

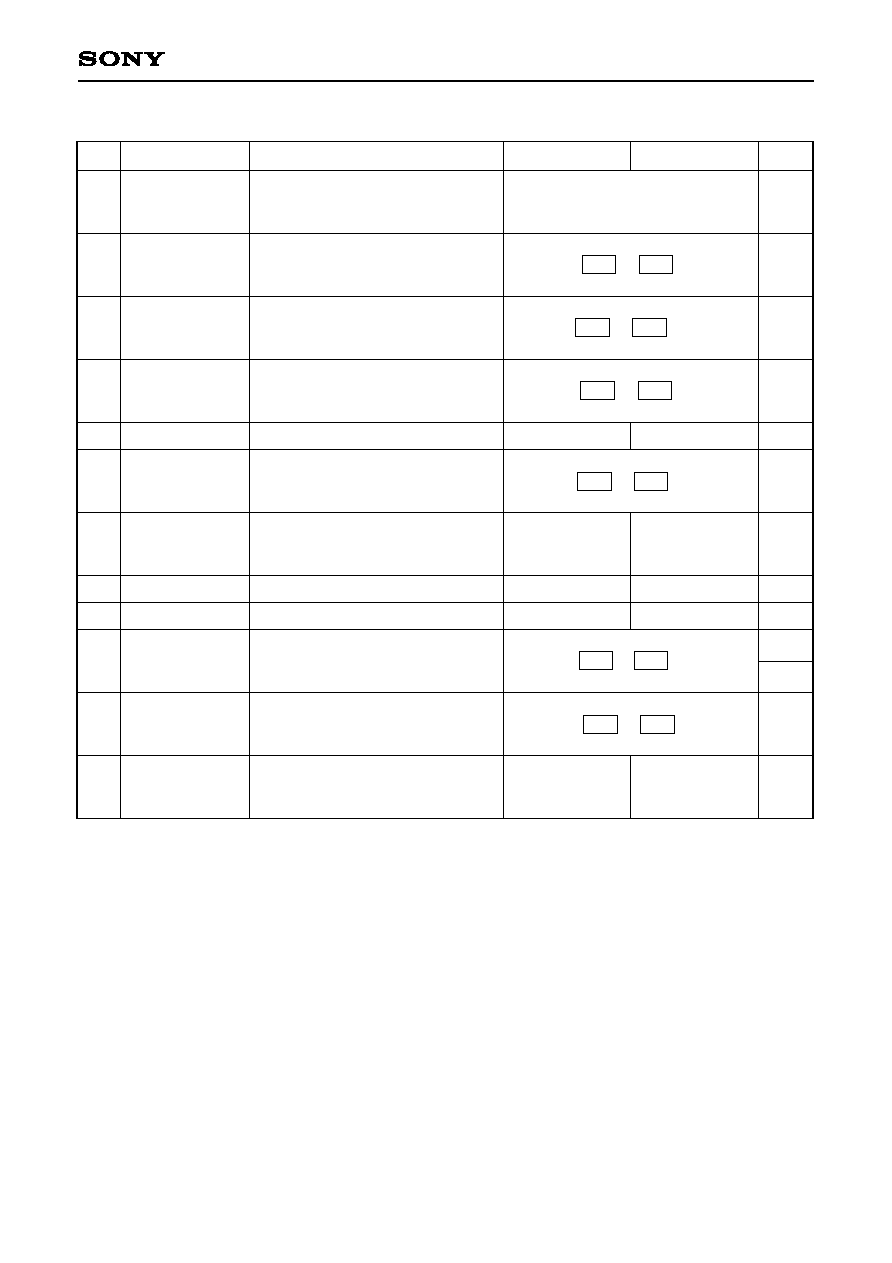

Pin Status Table

Pin

No.

A1

A2

A3

A4

A5

A6

A7

A8

A9

B1

B2

B3

B4

B5

B6

B7

B8

B9

C1

C2

C3

C4

C5

C6

C7

C8

C9

D1

D2

NC

NC

SCK2

SSI2

TEST3

AV

SS4

C8

AV

SS6

AV

DD5

D2

D1

D0

SEN2

TEST5

AV

DD4

C7

AV

DD3

AV

SS3

D5

D4

D3

TEST4

AV

SS5

C9

C3

C4

CCDIN

D8

D7

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

D3

D7

D8

D9

E1

E2

E3

E7

E8

E9

F1

F2

F3

F7

F8

F9

G1

G2

G3

G7

G8

G9

H1

H2

H3

H7

H8

H9

J1

D6

C1

C2

AV

SS1

D9

DV

DD1

DV

SS1

AV

SS2

AV

DD2

AV

DD1

DV

SS2

DV

SS3

DV

DD2

PBLKI

XSHDI

XSHPI

ADCLKI

CLPOBI

CLPDMI

PBLK

XSHD

XSHP

ADCLK

CLPOB

CLPDM

XRS

V

DD4

V

DD3

CKI

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

--

ACT

L

L

H

ACT

L

L

ACT

ACT

L

L

ACT

ACT

L

L

ACT

ACT

L

L

H

ACT

L

L

H

ACT

L

L

ACT

--

--

ACT

ACT

ACT

ACT

Symbol

Pin

No.

Symbol

CAM

SLP

RST

STB

CAM

SLP

RST

STB

≠ 18 ≠

CXD3406GA

1

It is for output. For input, all items are "ACT".

Note) ACT means that the circuit is operating, and DIS means that loading is stopped.

L indicates a low output level, and H a high output level in the controlled status.

Also, VH, VM and VL indicate the voltage levels applied to VH (Pin M5), VM (Pin L4) and VL (Pin M6),

respectively, in the controlled status.

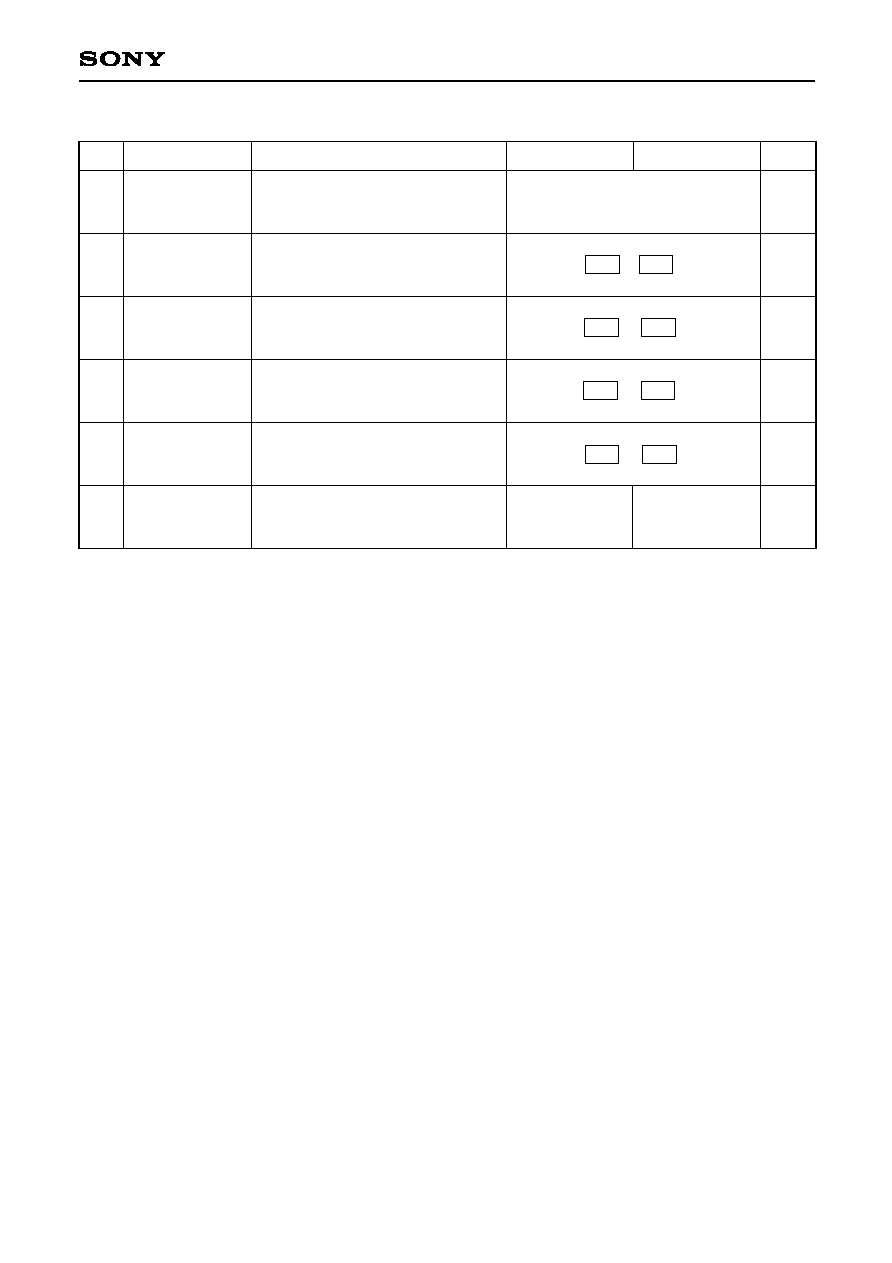

Pin

No.

J2

J3

J7

J8

J9

K1

K2

K3

K7

K8

K9

L1

L2

L3

L4

L5

L6

L7

L8

CKO

V

SS5

V

SS3

H1

H2

OSCO

MCKO

V

DD5

V

DD2

RG

V

SS2

OSCI

SSI1

V

SS4

VM

V1A

V3A

V

SS1

SSGSL

ACT

ACT

L

ACT

--

--

ACT

L

L

ACT

ACT

L

L

ACT

ACT

ACT

ACT

ACT

ACT

ACT

L

ACT

--

--

ACT

L

L

ACT

--

ACT

ACT

ACT

ACT

ACT

ACT

ACT

DIS

--

--

ACT

VH

VH

VM

ACT

VH

VH

VL

--

ACT

ACT

ACT

ACT

L9

M1

M2

M3

M4

M5

M6

M7

M8

M9

N1

N2

N3

N4

N5

N6

N7

N8

N9

V

DD1

SCK1

VD

1

TEST1

V2

VH

VL

TEST2

RST

WEN

SEN1

HD

1

V

SS6

V4

V1B

V3B

SUB

SNCSL

ID

--

ACT

ACT

ACT

DIS

ACT

L

L

H

--

ACT

VM

VM

VM

--

--

--

ACT

ACT

ACT

L

ACT

L

L

L

ACT

ACT

ACT

DIS

ACT

L

L

H

--

ACT

VM

VM

VL

ACT

VH

VH

VM

ACT

VH

VH

VL

ACT

VH

VH

VL

ACT

ACT

ACT

ACT

ACT

L

L

L

Symbol

Pin

No.

Symbol

CAM

SLP

RST

STB

CAM

SLP

RST

STB

≠ 19 ≠

CXD3406GA

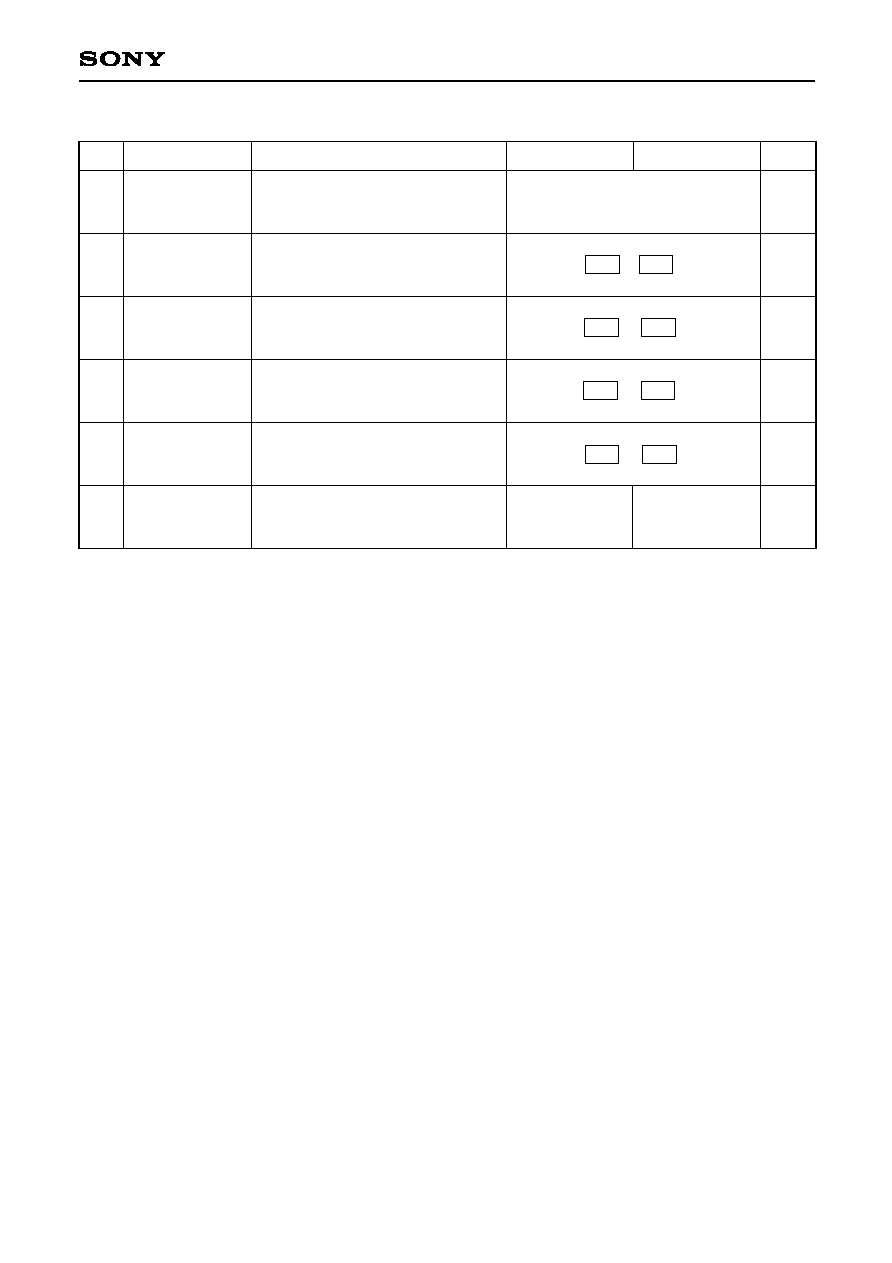

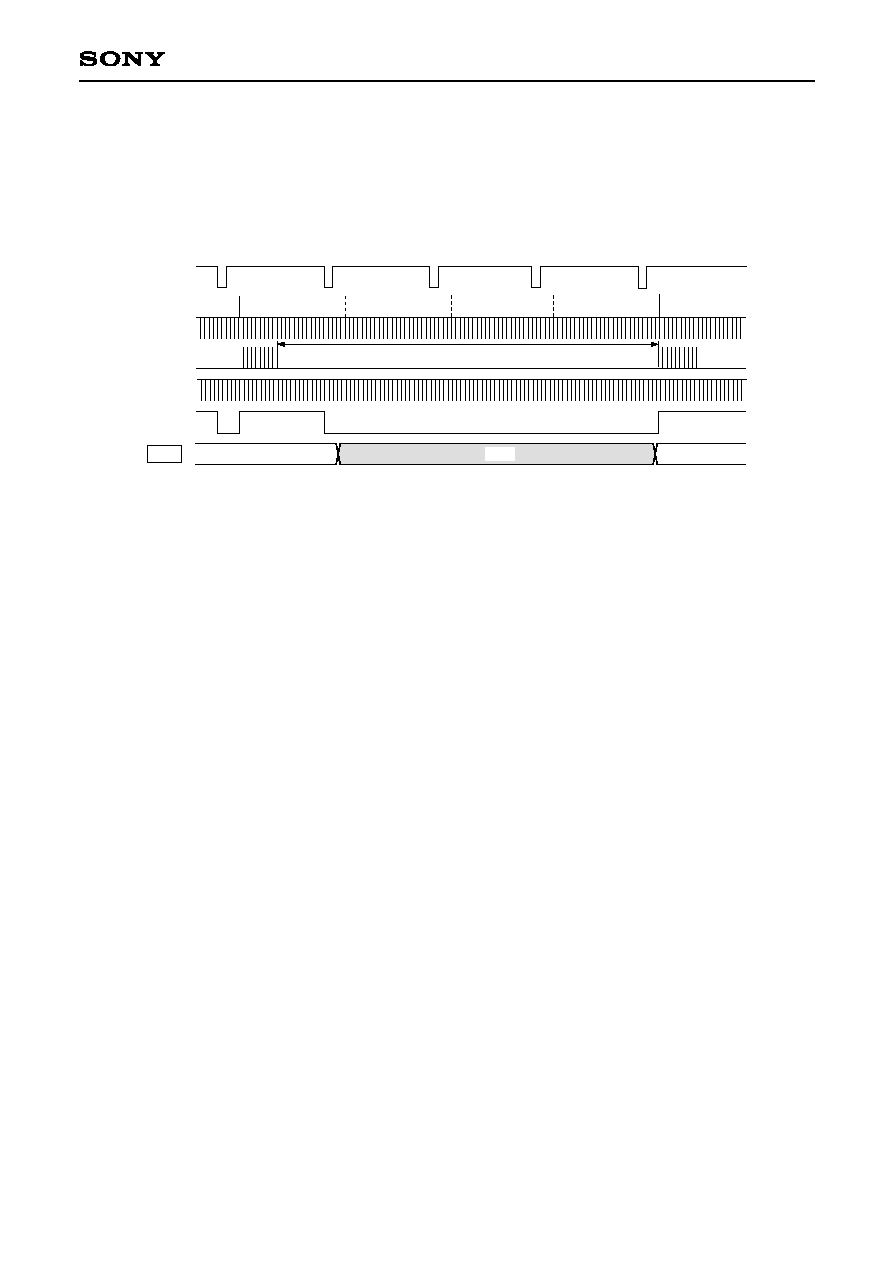

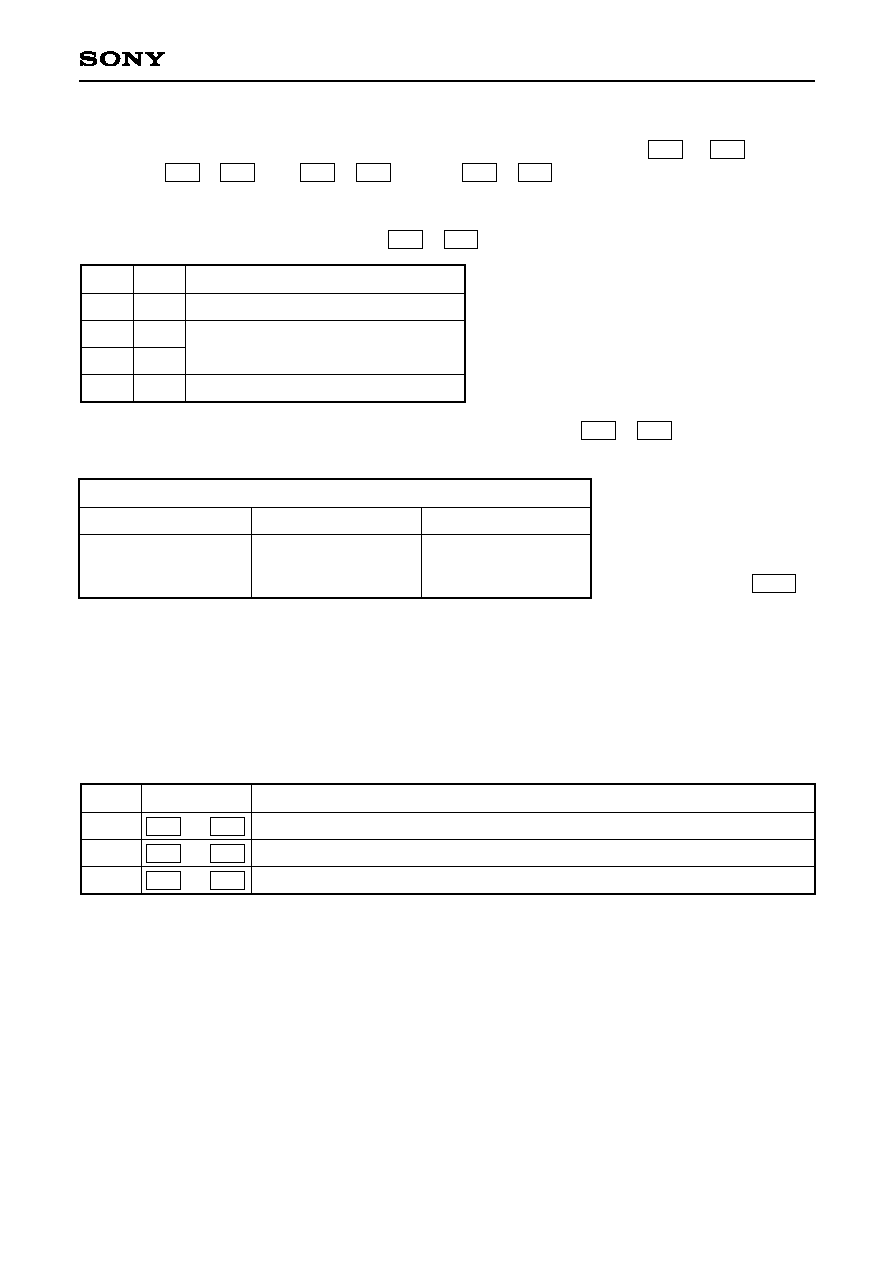

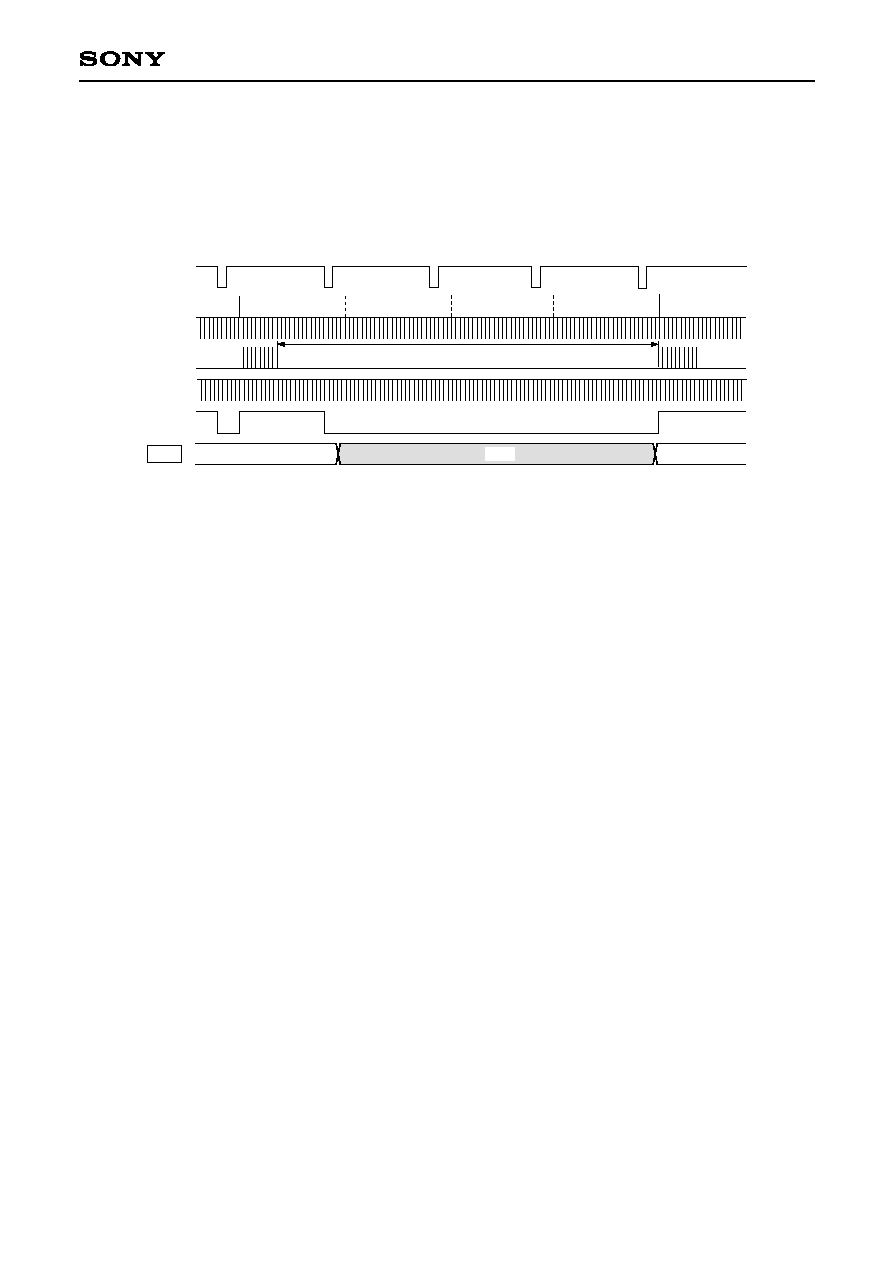

Timing Generator Block Serial Interface Control

The CXD3406GA's timing generator block basically loads and reflects the timing generator block serial

interface data sent in the following format in the readout portion at the falling edge of HD. Here, readout portion

specifies the horizontal period during which V1A/B and V3A/B, etc. take the ternary value.

Note that some items reflect the timing generator block serial interface data at the falling edge of VD or the

rising edge of SEN1.

00

01

02

03

04

05

06

07

41

42

43

44

45

46

47

SSI1

SCK1

SEN1

There are two categories of timing generator block serial interface data: CXD3406GA timing generator block

drive control data (hereafter "control data") and electronic shutter data (hereafter "shutter data").

The details of each data are described below.

≠ 20 ≠

CXD3406GA

Control Data

Data

D00

to

D07

D08

to

D09

D10

to

D12

D13

to

D14

D15

D16

to

D23

D24

to

D33

D34

D35

D36

to

D37

D38

to

D39

D40

to

D47

Symbol

CHIP

CTG

MODE

SMD

PTSG

CDAT

--

--

--

LDAD

STB

--

Function

Chip enable

Category switching

Drive mode switching

Electronic shutter mode switching

Internal SSG output pattern switching

AF drive control data

--

--

--

ADCLK logic phase switching

Standby control

--

Data = 0

Data = 1

10000001

Enabled

Other values

Disabled

See D08 to D09 CTG.

See D10 to D12 MODE.

See D13 to D14 SMD.

NTSC equivalent

PAL equivalent

See D16 to D23 CDAT.

--

--

--

--

--

--

See D36 to D37 LDAD.

See D38 to D39 STB.

--

--

RST

All

0

All

0

All

0

All

0

0

All

0

All

0

1

0

All

0

All

0

1

0

≠ 21 ≠

CXD3406GA

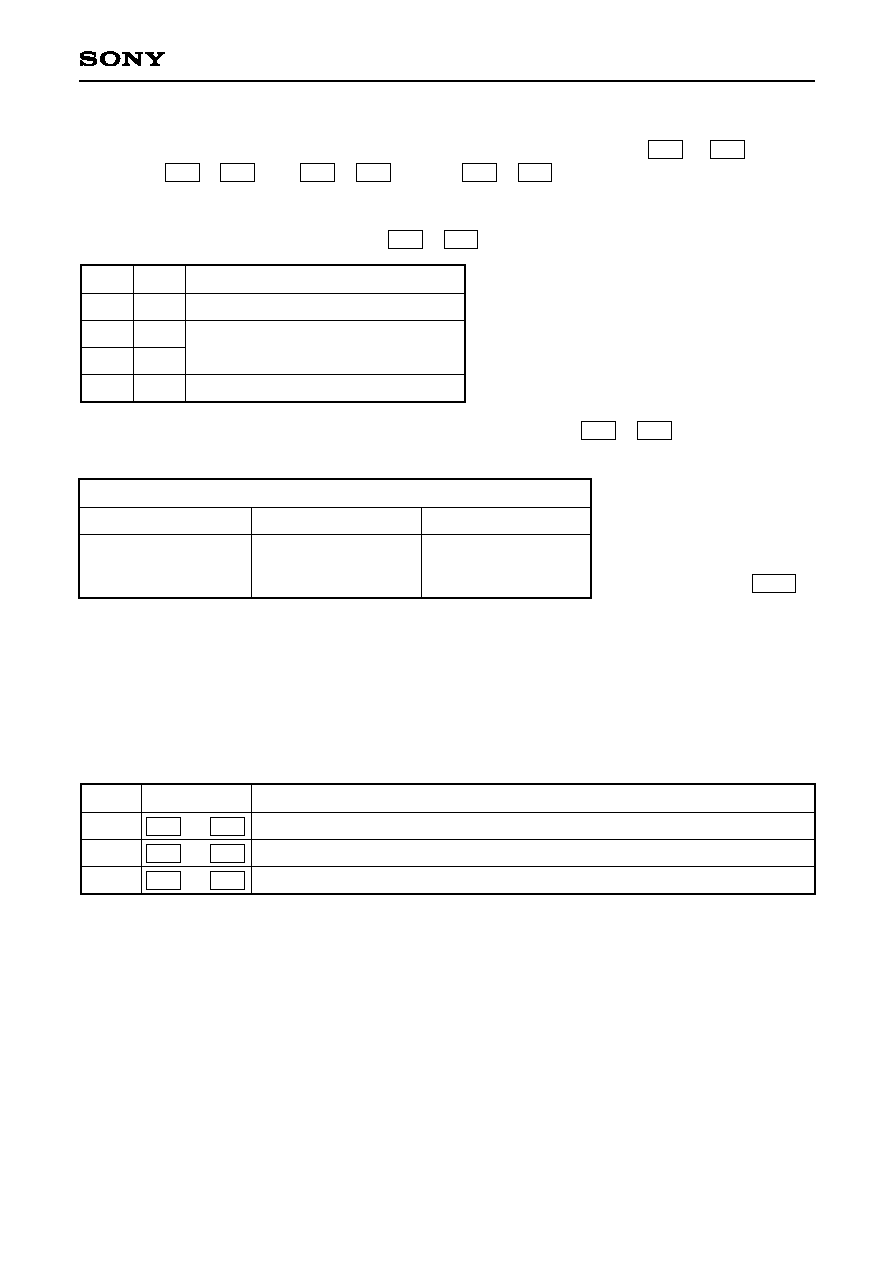

Shutter Data

Data

D00

to

D07

D08

to

D09

D10

to

D19

D20

to

D31

D32

to

D41

D42

to

D47

Symbol

CHIP

CTG

SVD

SHD

SPL

--

Function

Chip enable

Category switching

Electronic shutter vertical period

specification

Electronic shutter horizontal period

specification

High-speed shutter position

specification

--

Data = 0

Data = 1

10000001

Enabled

Other values

Disabled

See D08 to D09 CTG.

See D10 to D19 SVD.

See D20 to D31 SHD.

See D32 to D41 SPL.

--

--

RST

All

0

All

0

All

0

All

0

All

0

All

0

≠ 22 ≠

CXD3406GA

Detailed Description of Each Data

Shared data: D08 to D09 CTG [Category]

Of the data provided to the CXD3406GA by the timing generator block serial interface, the CXD3406GA loads

D10 and subsequent data to each data register as shown in the table below according to the combination of

D08 and D09 .

D09

0

0

1

D08

0

1

X

Description of operation

Loading to control data register

Loading to shutter data register

Test mode

D11

0

0

1

1

0

1

D12

0

0

0

0

1

1

D10

0

1

0

1

X

X

Description of operation

Draft mode (sextuple speed: default)

Frame mode (A field readout)

Frame mode (B Field readout)

Frame mode

AF1 mode

AF2 mode

Note that the CXD3406GA can apply these categories consecutively within the same vertical period. However,

care should be taken as the data is overwritten if the same category is applied.

Control data: D10 to D12 MODE [Drive mode]

The CXD3406GA timing generator block drive mode can be switched as follows. However, the drive mode bits

are loaded to the CXD3406GA and reflected at the falling edge of VD.

Control data: D15 PTSG [Internal SSG output pattern]

The CXD3406GA internal SSG output pattern can be switched as follows. However, the drive mode bits are

loaded to the CXD3406GA and reflected at the falling edge of VD.

D15

0

1

Description of operation

NTSC equivalent pattern

PAL equivalent pattern

The VD period in each pattern is defined as follows for each drive mode.

1

Only 944H and 945H are 1208ck period.

See the Timing Charts for the actual operation.

NTSC equivalent pattern

PAL equivalent pattern

Frame mode

918H + 1716ck

945H

1

Draft mode

262H + 1144ck

314H + 1568ck

AF1 mode

131H + 572ck

157H + 784ck

AF2 mode

65H + 1430ck

78H + 1536ck

≠ 23 ≠

CXD3406GA

Control data: D36 to D37 LDAD [ADCLK logic phase]

This indicates the ADCLK logic phase adjustment data. The default is 90∞ relative to MCKO.

Control data: D38 to D39 STB [Standby]

The operating mode of the timing generator block is switched as follows. However, the standby bits are loaded

to the CXD3406GA and control is applied immediately at the rising edge of SEN1.

D37

0

0

1

1

D36

0

1

0

1

Degree of adjustment (∞)

0

90

180

270

D39

X

0

1

D38

0

1

1

Symbol

CAM

SLP

STB

Operating mode

Normal operating mode

Sleep mode

Standby mode

See the Pin Status Table for the pin status in each mode.

≠ 24 ≠

CXD3406GA

The frame shift data is expressed as shown in the table below using D16 to D23 CDAT.

MSB

LSB

D23

D22

D21

D20

D19

D18

D17

D16

0

1

1

0

6

1

0

0

1

9

CDAT is expressed as 69h .

Its definition area is specified as follows.

AF1 mode: 00h

CDAT

FFh (11 to 23H)

AF2 mode: 00h

CDAT

FFh (14 to 27H)

Control data: [AF drive]

The CXD3406GA controls the drive of the vertical cut-out area of the line in AF1/AF2 mode by using control

data D16 to D23 CDAT. This mode has a function on purpose to raise frame rate for auto focus (AF), and

cannot support operation such as electrical image stabilization.

The AF drive bits are loaded to the CXD3406GA and reflected at the falling edge of VD. As shown in the figure

below, first, the fixed stage is swept at high speed, and it goes to readout period and vertical OB period. Then

normal transfer is performed equivalent to draft mode from the frame shift to the stage specified by the serial

interface data to the timing of the falling edge of the next VD.

Therefore, the number of frame shift stages applied to CDAT and the control by VD period are conditions for

its application.

VD

0

V1A

Vck

MODE

00h

FFh

CDAT

4

0

00h

Frame shift

Normal transfer

High-speed sweep

The number of high-speed sweep are different according to the selected mode. They are specified as follows.

AF1 mode: 138 stages (0 to 7H)

AF2 mode: 208 stages (0 to 11H)

≠ 25 ≠

CXD3406GA

Control data/shutter data: [Electronic shutter]

The CXD3406GA realizes various electronic shutter functions by using control data D13 to D14 SMD and

shutter data D10 to D19 SVD, D20 to D31 SHD and D32 to D41 SPL.

These functions are described in detail below.

First, the various modes are shown below.

These modes are switched using control data D13 to D14 SMD.

D14

0

0

1

1

D13

0

1

0

1

Description of operation

Electronic shutter stopped mode

High-speed/low-speed shutter mode

HTSG control mode

The electronic shutter data is expressed as shown in the table below using D20 to D31 SHD as an example.

However, MSB (D31) is a reserve bit for the future specification, and it is handled as a dummy on this IC.

MSB

LSB

D29

D28

D31

D30

D27

D26

D25

D24

D23

D22

D21

D20

1

1

0

0

C

X

0

0

1

1

0

0

1

1

3

SHD is expressed as 1C3h .

[Electronic shutter stopped mode]

During this mode, all shutter data items are invalid.

SUB is not output in this mode, so the shutter speed is the accumulation time for one field.

[High-speed/low-speed shutter mode]

During this mode, the shutter data items have the following meanings.

The period during which SVD and SHD are specified together is the shutter speed. Concretely, when

specifying high-speed shutter, SVD is set to "000h". (See the figure.) During low-speed shutter, or in other

words when SVD is set to "001h" or higher, the serial interface data is not loaded until this period is finished.

The vertical period indicated here corresponds to one field in each drive mode. In addition, the number of

horizontal periods applied to SHD can be considered as (number of SUB pulses ≠ 1). However, in the frame

mode A field, it matches (number of SUB pulses + 1). This is a specification for flickerless when the same

mode is repeated. But this change may not occur because of flickerless depending on the conditions during

low-speed shutter.

Note) The bit data definition area is assured in terms of the CXD3406GA functions, and does not assure the

CCD characteristics.

Symbol

SVD

SHD

SPL

Data

D10 to D19

D20 to D31

D32 to D41

Description

Number of vertical periods specification (000h

SVD

3FFh)

Number of horizontal periods specification (000h

SHD

7FFh)

Vertical period specification for high-speed shutter operation (000h

SPL

3FFh)

≠ 26 ≠

CXD3406GA

VD

SHD

01

V1A

SUB

WEN

SMD

000h

002h

SVD

050h

10Fh

SHD

01

SVD

VD

SPL

SHD

01

V1A

SUB

WEN

SMD

000h

001h

SPL

000h

002h

SVD

0A3h

10Fh

SHD

10

SVD

Further, SPL can be used during this mode to specify the SUB output at the desired vertical period during the

low-speed shutter period.

In the case below, SUB is output based on SHD at the SPL vertical period out of (SVD + 1) vertical periods.

Incidentally, SPL is counted as "000h", "001h", "002h" and so on in conformance with SVD.

Using this function, it is possible to achieve smooth exposure time transitions when changing from low-speed

shutter to high-speed shutter or vice-versa.

≠ 27 ≠

CXD3406GA

VD

V1A

SUB

WEN

01

11

Exposure time

01

SMD

Vck

[HTSG control mode]

During this mode, all shutter data items are invalid.

The V1A/B and V3A/B ternary level outputs are stopped, so the shutter speed is the value obtained by adding

the shutter speed specified in the preceding vertical period to the vertical period during which these readout

pulses are stopped as shown in the figure.

≠ 28 ≠

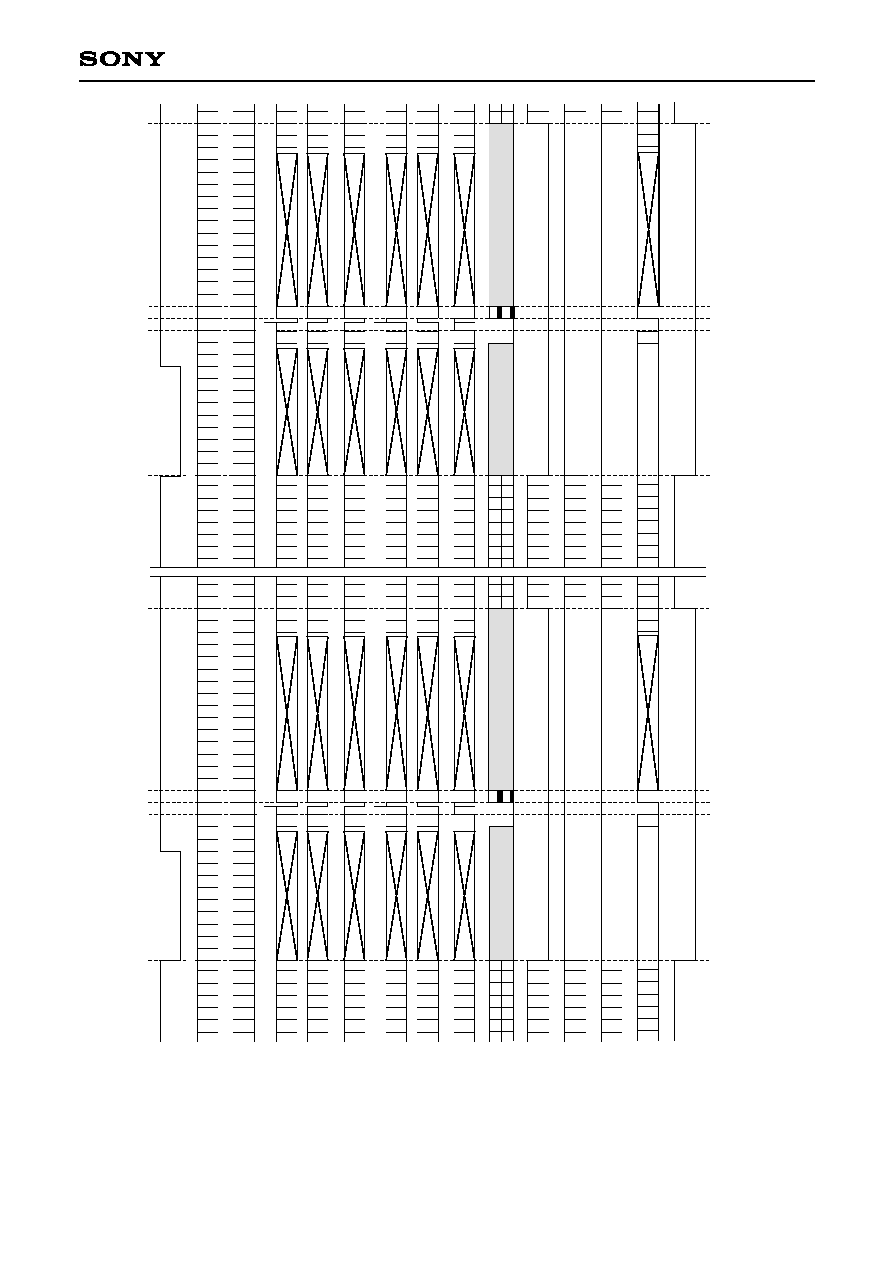

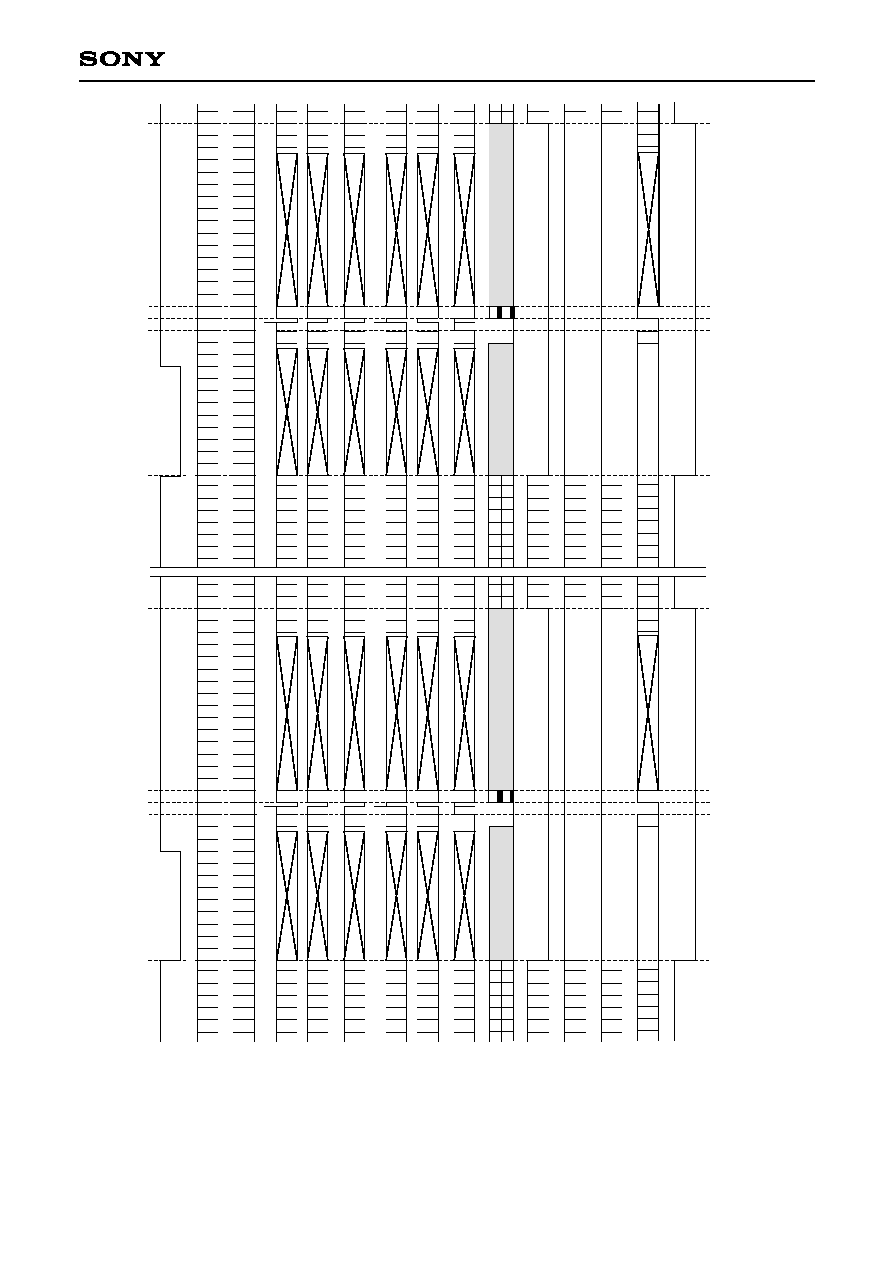

CXD3406GA

VD

SUB

CLPOB

CLPDM

V1A

C

High-speed sweep block

High-speed sweep block

C

V1B

V2

V3A

V3B

V4

CCD OUT

1547

1549

1542

1544

1546

1548

1550

1539

1541

1543

1545

3

1

57

24682

6

4

81

0

1

2

13579

1

1

1

3

1

5

PBLK

ID

WEN

A

Field

B Field

HD

918

1

29

34

12

8

3

4

918

810

810

A

B

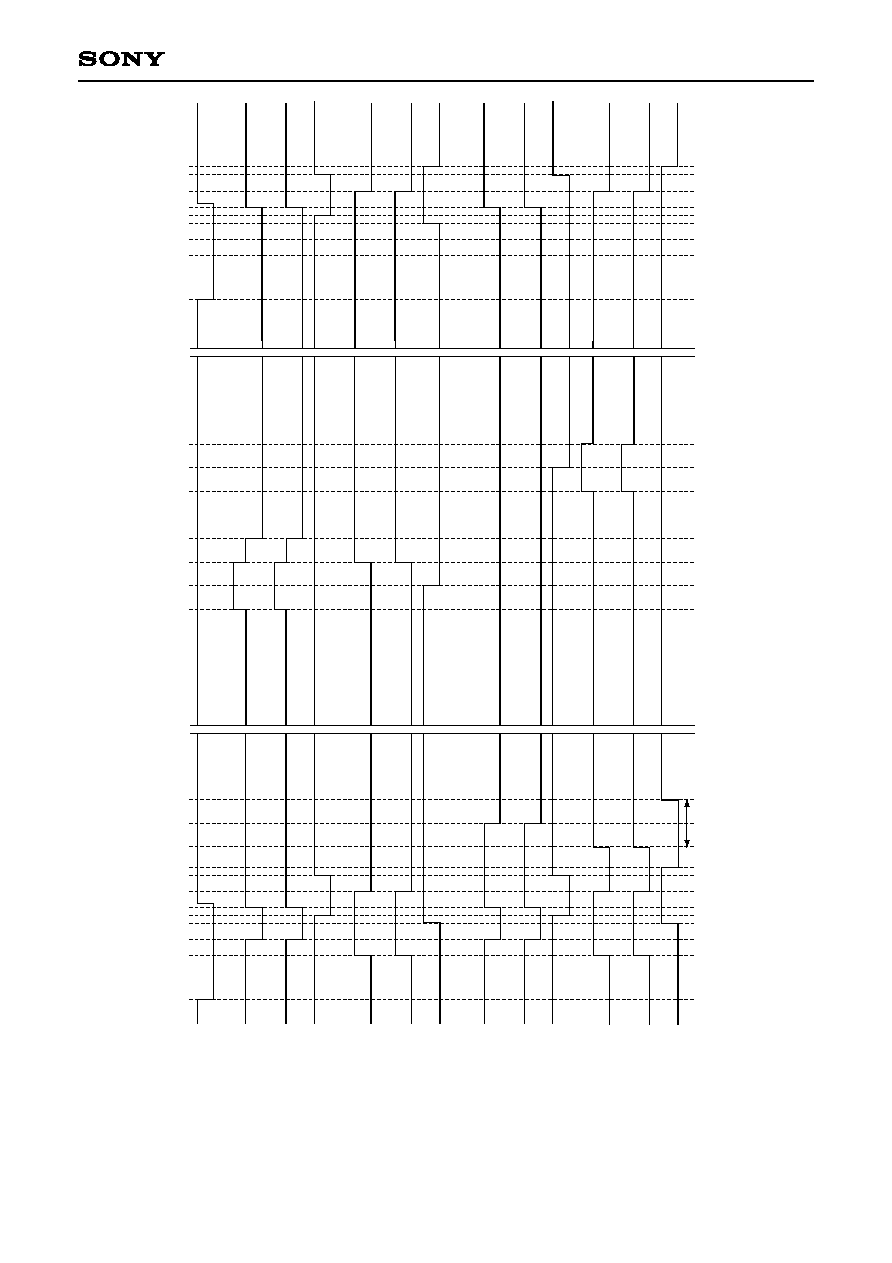

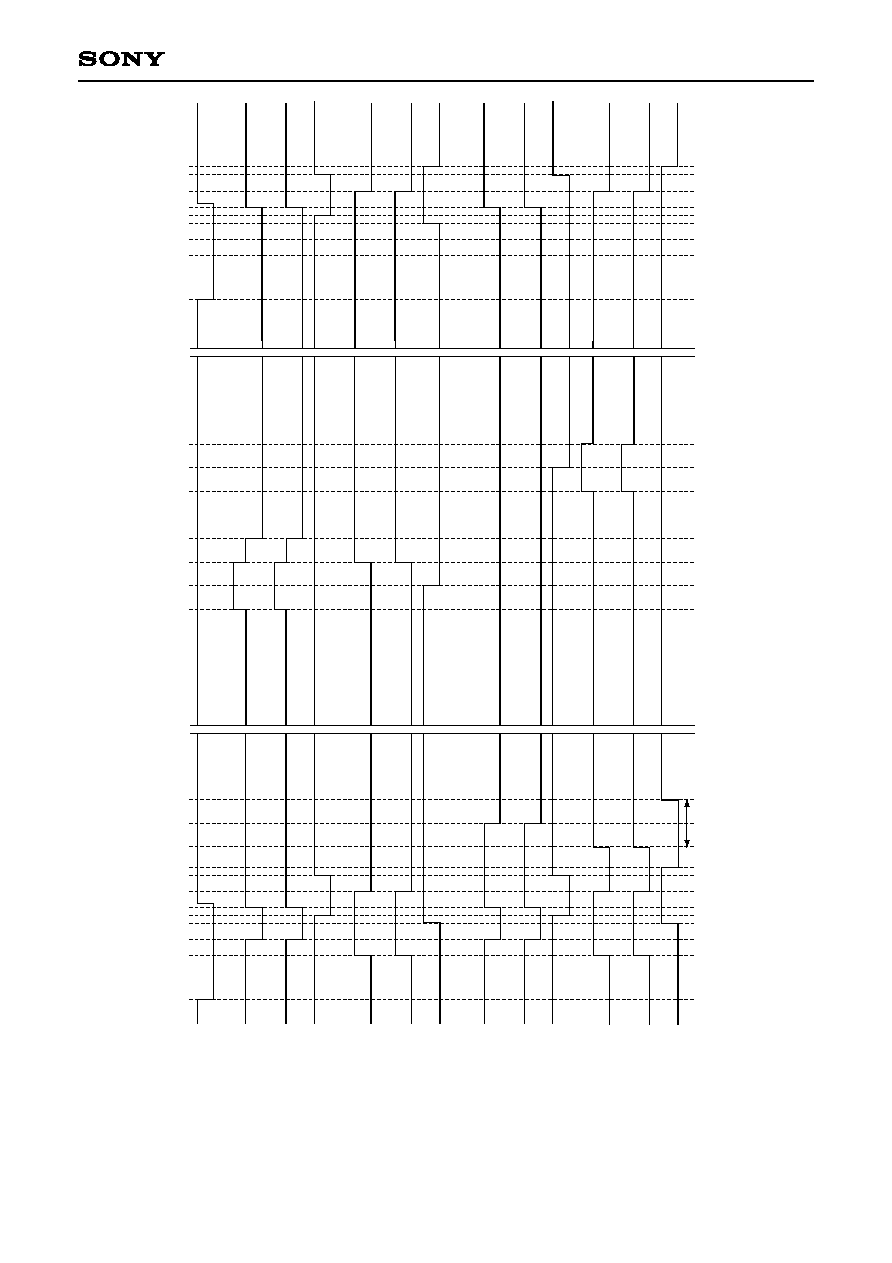

The number of SUB pulses is determined by the serial interface data. This chart shows the case where SUB pulses are output in e

ach horizontal period.

ID is low for lines where CCD OUT contains the R component, and high for lines where CCD OUT contains the B component.

VD of this chart is NTSC equivalent pattern (918H + 1716ck units). For PAL equivalent pattern, it is 945H units, but 1208ck per

iod only for 944H and 945H.

Chart-1 Vertical Direction Timing Chart

MODE

Frame mode

Applicable CCD image sensor

∑

ICX252/262

≠ 29 ≠

CXD3406GA

VD

HD

SUB

V1A

V2

V3A

V3B

V4

CLPOB

CLPDM

ID

PBLK

V1B

CCD OUT

15

10

3

6

22

27

34

13

8

1

4

20

546

539

534

527

544

537

532

525

549

25

32

10

3

6

15

22

27

34

8

1

4

13

20

25

32

546

539

534

527

544

537

532

525

549

WEN

2

1

262

261

2

1

262

261

D

D

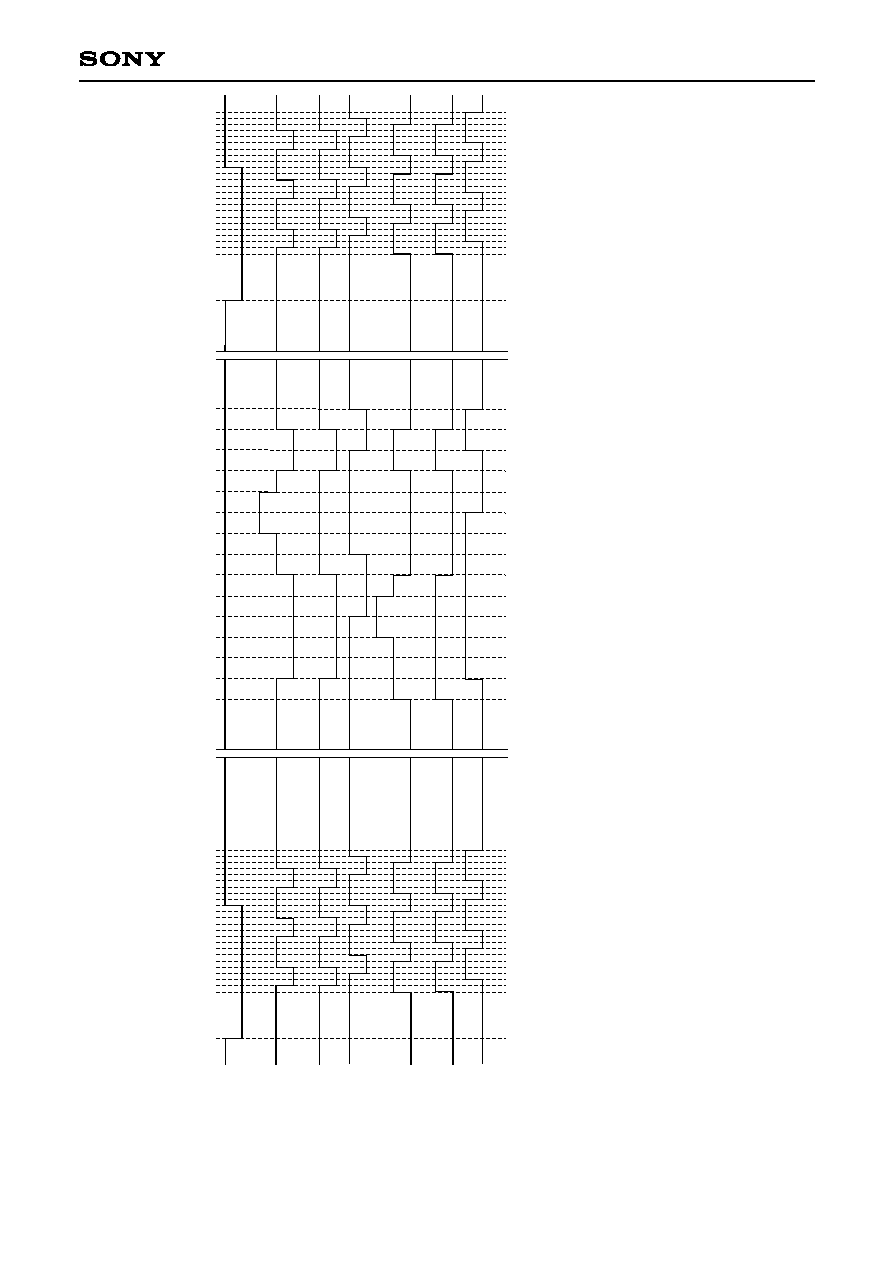

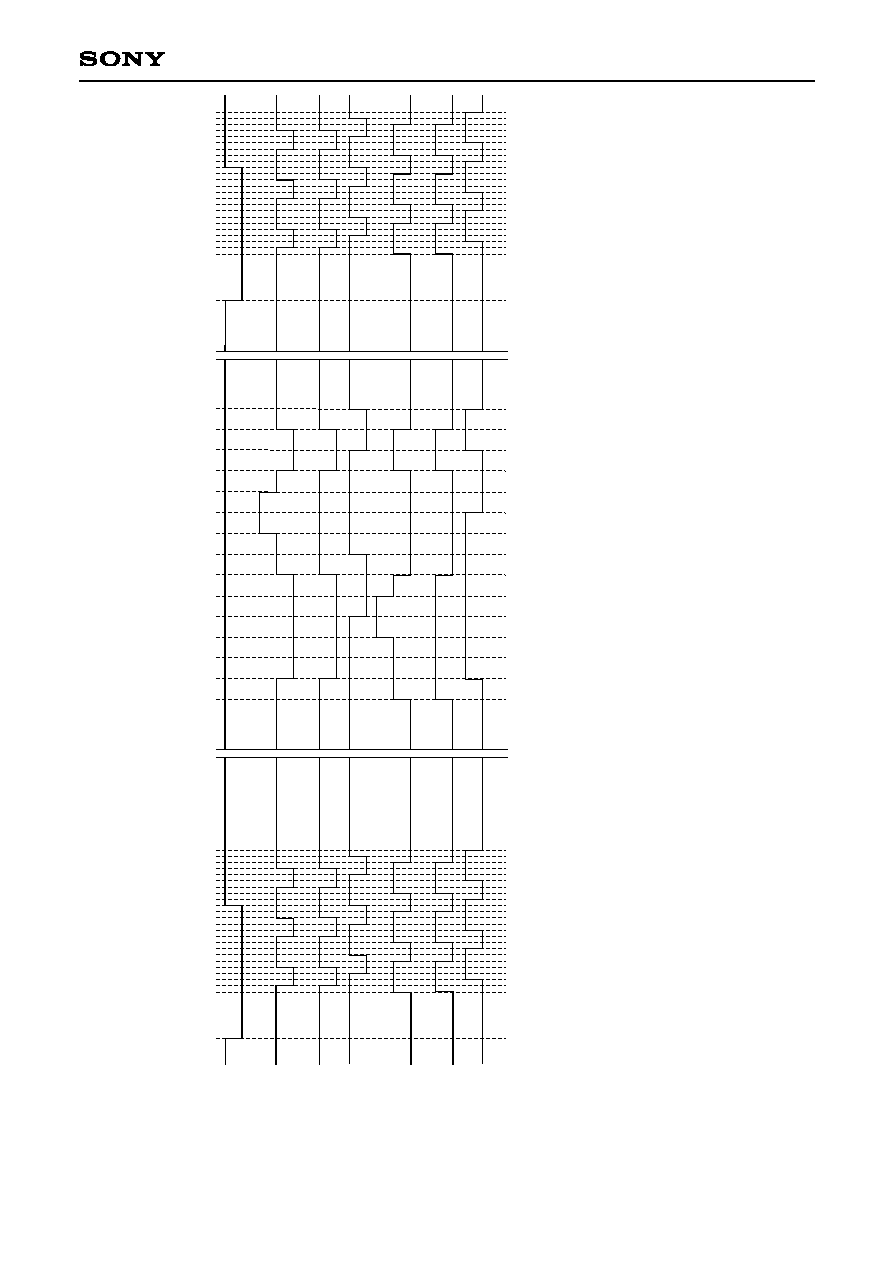

The number of SUB pulses is determined by the serial interface data. This chart shows the case where SUB pulses are output in e

ach horizontal period.

ID is low for lines where CCD OUT contains the R component, and high for lines where CCD OUT contains the B component.

VD of this chart is NTSC equivalent pattern (262H + 1144ck units). For PAL equivalent pattern, it is 314H + 1568ck units.

Chart-2 Vertical Direction Timing Chart

MODE

Draft mode

Applicable CCD image sensor

∑

ICX252/262

≠ 30 ≠

CXD3406GA

VD

CCD OUT

6

4

6

4

WEN

HD

ID

CLPOB

CLPDM

PBLK

V1A

V1B

V2

V3B

V4

SUB

V3A

10

25

1

8

131

10

25

1

8

131

High-speed

sweep block

High-speed

sweep block

Frame shift block

FD

G

Frame shift block

F

D

G

The number of SUB pulses is determined by the serial interface data. This chart shows the case where SUB pulses are output in e

ach horizontal period.

ID is low for lines where CCD OUT contains the R component, and high for lines where CCD OUT contains the B component.

138 stages are fixed for high-speed sweep block ; 0 to 255 stages can be specified by the serial interface for the frame shift

block.

VD of this chart is NTSC equivalent pattern (131H + 572ck units). For PAL equivalent pattern, it is 157H + 784ck units.

Chart-3 Vertical Direction Timing Chart

MODE

AF1 mode

Applicable CCD image sensor

∑

ICX252/262

≠ 31 ≠

CXD3406GA

VD

CCD OUT

6

4

6

4

WEN

HD

ID

CLPOB

CLPDM

PBLK

V1A

V1B

V2

V3B

V4

SUB

V3A

F

High-speed sweep block

Frame shift block

DG

F

High-speed sweep block

Frame shift block

D

G

14

29

1

12

65

14

29

1

12

65

The number of SUB pulses is determined by the serial interface data. This chart shows the case where SUB pulses are output in e

ach horizontal period.

ID is low for lines where CCD OUT contains the R component, and high for lines where CCD OUT contains the B component.

208 stages are fixed for high-speed sweep block ; 0 to 255 stages can be specified by the serial interface for the frame shift

block.

VD of this chart is NTSC equivalent pattern (65H + 1430ck units). For PAL equivalent pattern, it is 78H + 1536ck units.

Chart-4 Vertical Direction Timing Chart

MODE

AF2 mode

Applicable CCD image sensor

∑

ICX252/262

≠ 32 ≠

CXD3406GA

148

HD

MCKO

H1

H2

V1A/B

V2

V3A/B

V4

SUB

PBLK

CLPOB

CLPDM

(2288)

05

0

52

100

150

11

0

70

99

47

10

174

90

52

70

200

250

ID

WEN

198

172

198

157

128

11

0

11

0

138

52

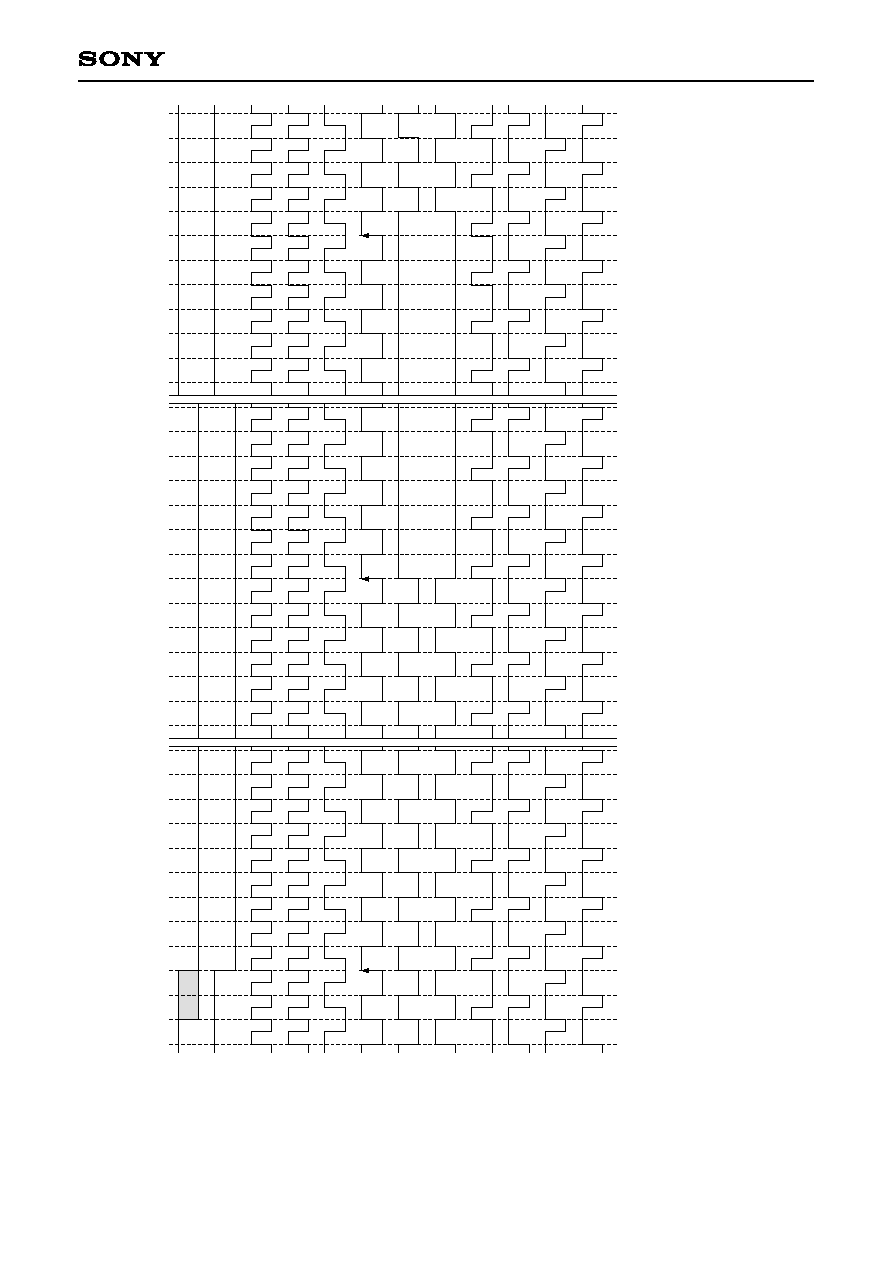

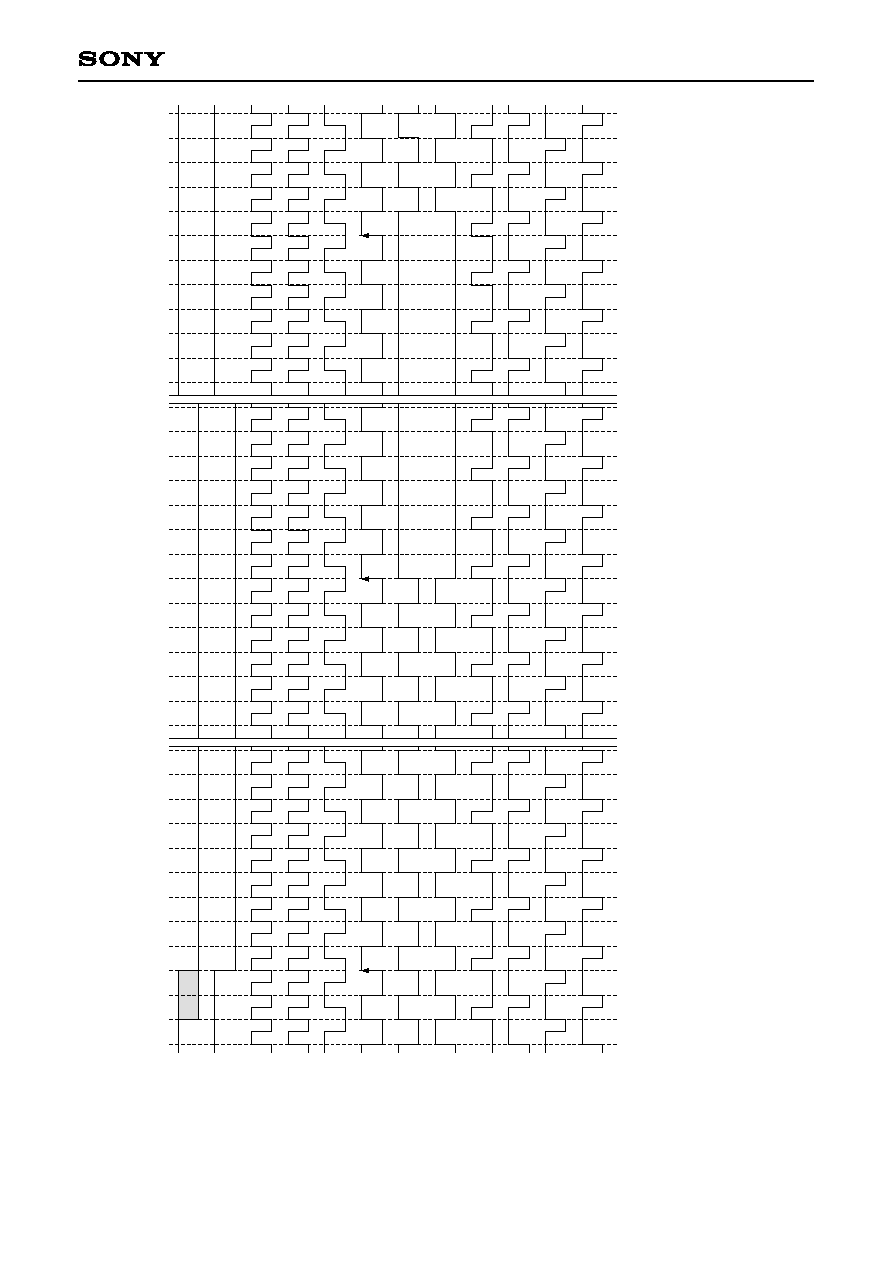

HD of this chart indicates the actual CXD3406GA load timing.

The numbers at the output pulse transition points indicate the count at the MCKO rise from the fall of HD.

The HD fall period should be between approximately 2.9 to 9.5µ

s

(when the drive frequency is 18MHz). This chart shows a period

of 115ck (6.4µ

s). Internal SSG is at this timing.

SUB is output at this timing shown above when output is controlled by the serial interface data.

ID and WEN are output at this timing shown above at the position shown in Chart-1.

Chart-5 Horizontal Direction Timing Chart

MODE

Frame mode

Applicable CCD image sensor

∑

ICX252/262

≠ 33 ≠

CXD3406GA

HD

MCKO

H1

H2

V1A/B

V2

V3A/B

V4

SUB

PBLK

CLPOB

CLPDM

(2288)

05

0

52

100

150

70

106

93

66

47

10

174

52

200

250

ID

WEN

198

172

198

84

120

75

11

0

11

0

140

52

88

79

102

151

111

1

4

7

97

156

129

11

5

61

71

142

57

138

124

133

HD of this chart indicates the actual CXD3406GA load timing.

The numbers at the output pulse transition points indicate the count at the MCKO rise from the fall of HD.

The HD fall period should be between approximately 2.9 to 9.5µ

s

(when the drive frequency is 18MHz). This chart shows a period

of 115ck (6.4µ

s). Internal SSG is at this timing.

SUB is output at this timing shown above when output is controlled by the serial interface data.

ID and WEN are output at this timing shown above at the position shown in Charts-2, 3 and 4.

Chart-6 Horizontal Direction Timing Chart

MODE

Draft/AF1/AF2 mode

Applicable CCD image sensor

∑

ICX252/262

≠ 34 ≠

CXD3406GA

HD

MCKO

H1

H2

V1A/B

V2

V3A/B

V4

SUB

PBLK

CLPOB

CLPDM

(2288)

05

0

52

100

150

52

139

11

0

197

71

70

200

250

ID

WEN

172

100

129

138

52

81

100

129

1

1

0

168

187

274

158

168

226

158

139

#4

#3

#2

#1

81

255

274

245

216

187

71

216

245

197

255

226

HD of this chart indicates the actual CXD3406GA load timing.

The numbers at the output pulse transition points indicate the count at the MCKO rise from the fall of HD.

The HD fall period should be between approximately 2.9 to 9.5µ

s

(when the drive frequency is 18MHz). This chart shows a period

of 115ck (6.4µ

s). Internal SSG is at this timing.

SUB is output at this timing shown above when output is controlled by the serial interface data.

High-speed sweep of V1A/B, V2, V3A/B and V4 is performed up to 26H of 768ck(#1038).

Chart-7 Horizontal Direction Timing Chart

(High-speed sweep: C)

MODE

Frame mode

Applicable CCD image sensor

∑

ICX252/262

≠ 35 ≠

CXD3406GA

HD

MCKO

H1

H2

V1A/B

V2

V3A/B

V4

SUB

PBLK

CLPOB

CLPDM

(2288)

05

0

52

100

150

71

52

109

90

147

64

47

10

52

200

250

ID

WEN

172

83

121

140

71

105

11

0

140

52

90

128

83

102

140

159

197

254

109

147

166

102

159

178

216

223

261

280

273

128

204

242

121

235

273

261

216

223

178

185

166

64

185

204

242

197

#2

#1

235

254

219

71

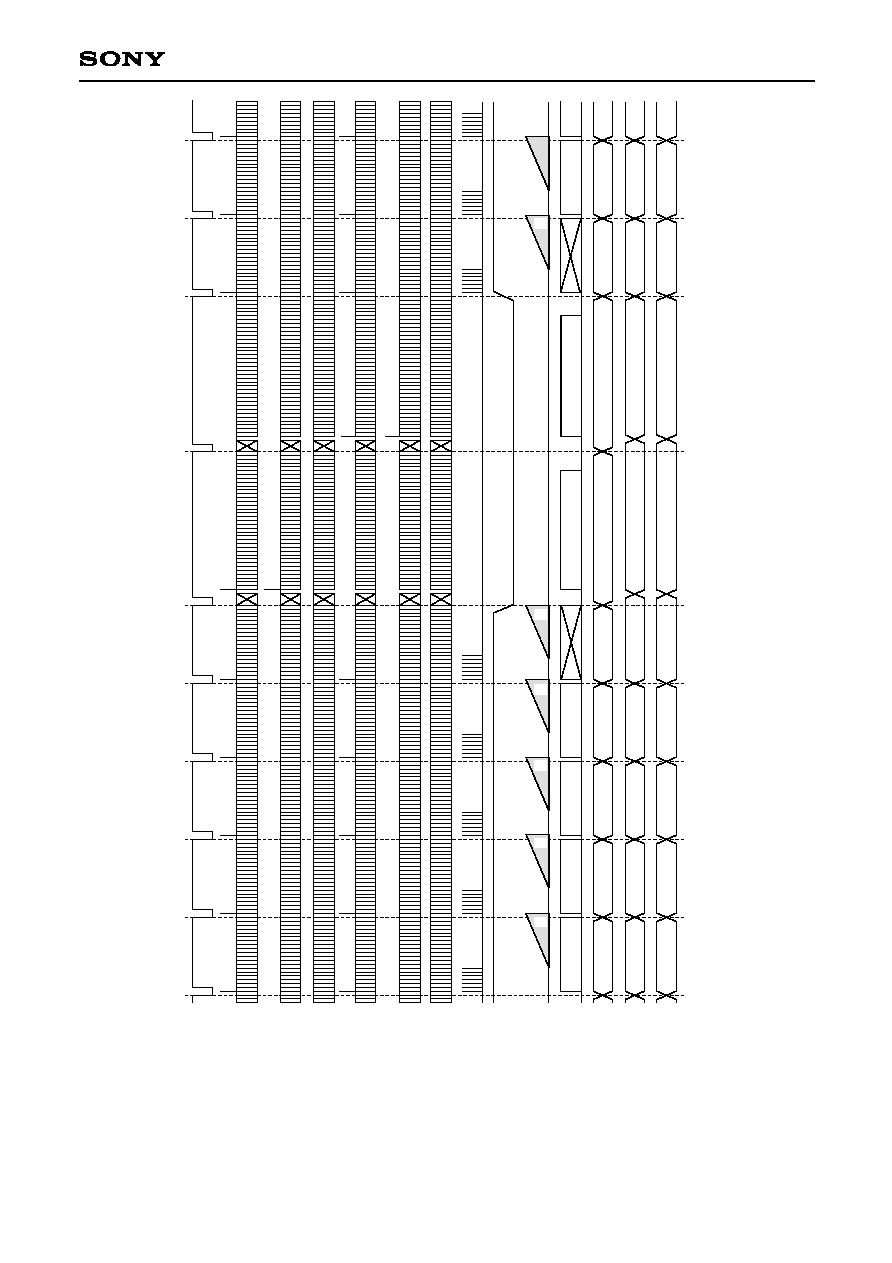

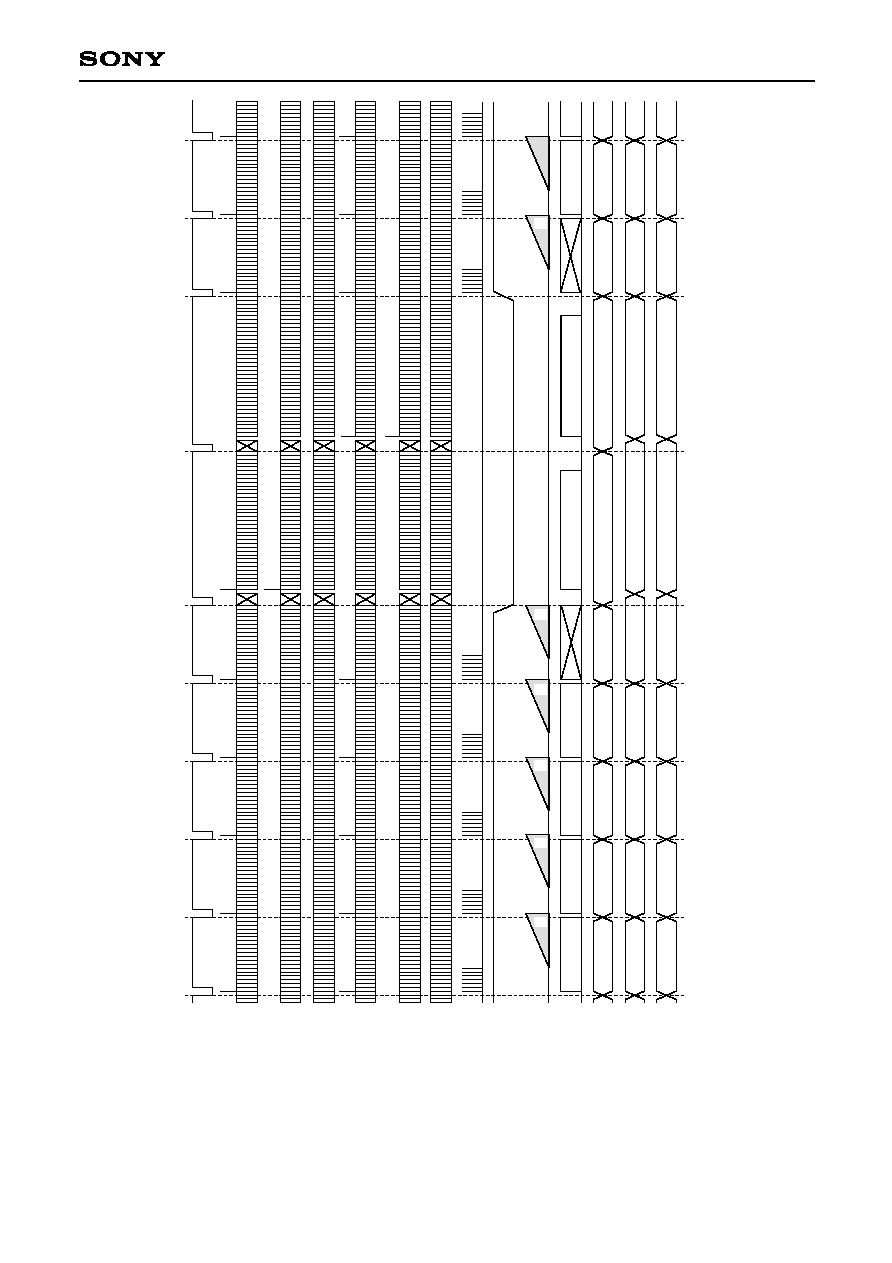

HD of this chart indicates the actual CXD3406GA load timing.

The numbers at the output pulse transition points indicate the count at the MCKO rise from the fall of HD.

The HD fall period should be between approximately 2.9 to 9.5µ

s

(when the drive frequency is 18MHz). This chart shows a period

of 115ck (6.4µ

s). Internal SSG is at this timing.

SUB is output at this timing shown above when output is controlled by the serial interface data.

WEN is output at this timing shown above at the position shown in Chart-3 and 4.

High-speed sweep of V1A/B, V2, V3A/B and V4 is performed up to 6H of 2056ck (#138) in AF1 mode and 10H of 884ck (#208) in AF2

mode.

Frame shift of V1A/B, V2, V3A/B and V4 receives the output control by the serial interface data and can specify up to #255 for

both of AF1/AF2 mode.

ID is output at the timing shown with dotted line during frame shift.

Chart-8 Horizontal Direction Timing Chart

(High-speed sweep: F)

(Frame shift: G)

MODE

AF1/AF2 mode

Applicable CCD image sensor

∑

ICX252/262

≠ 36 ≠

CXD3406GA

HD

[A

Field]

[B Field]

[A]

[B]

V3B

V4

V3B

V4

V1A

V1B

V2

V3A

V1A

V1B

V2

V3A

(2288)

0

52

70

110

90

128

99

148

157

181

211

241

(2288)

0

52

70

128

90

148

99

110

157

1100

1130

1160

1190

1280

1310

1250

Logic alignment portion

HD of this chart indicates the actual CXD3406GA load timing.

The numbers at the output pulse transition points indicate the count at the MCKO rise from the fall of HD.

The HD fall period should be between approximately 2.9 to 9.5µ

s

(when the drive frequency is 18MHz). This chart shows a period

of 115ck (6.4µ

s). Internal SSG is at this

timing.

Chart-9 Horizontal Direction Timing Chart

MODE

Frame mode

Applicable CCD image sensor

∑

ICX252/262

≠ 37 ≠

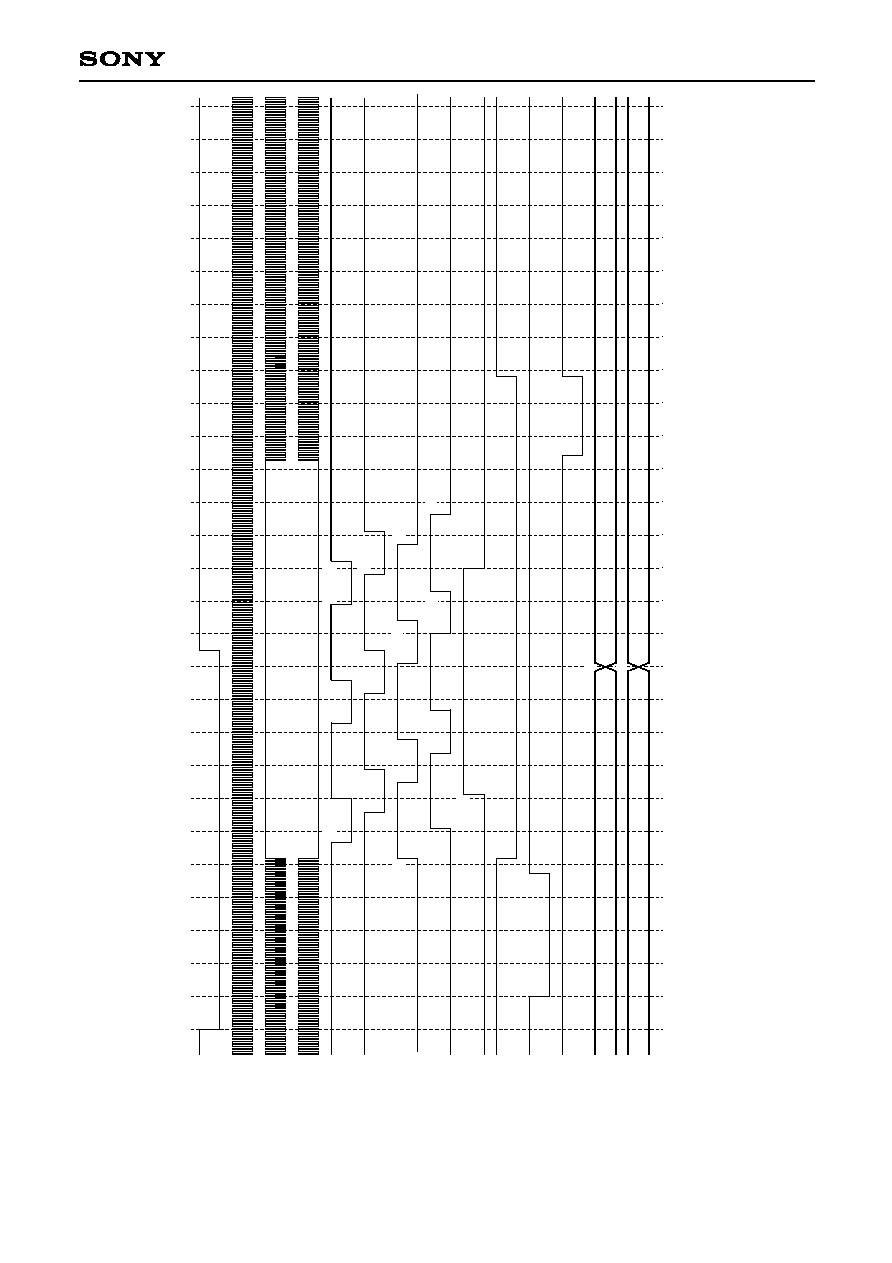

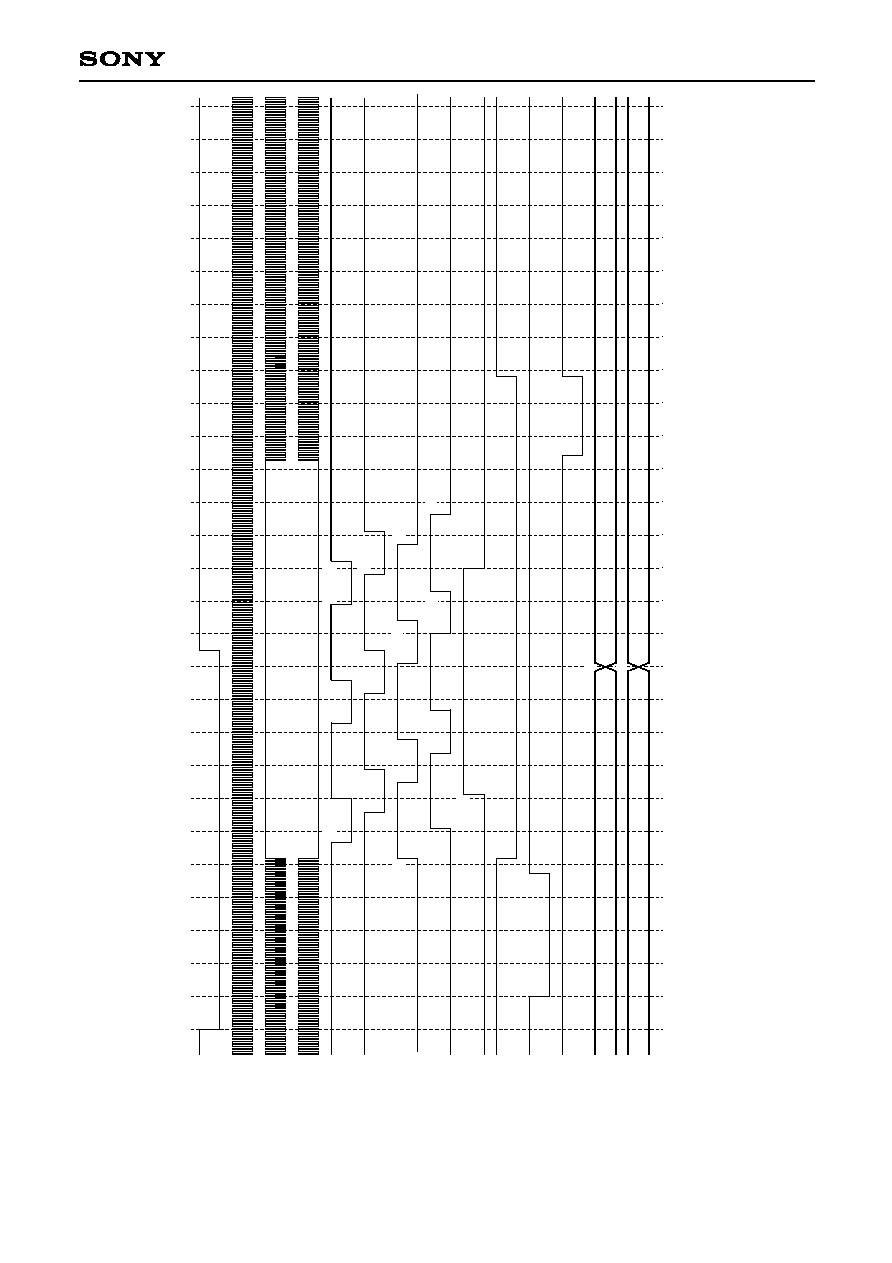

CXD3406GA

52

57

61

66

70

75

79

84

88

93

97

102

106

111

115

120

124

129

133

138

142

147

151

156

52

57

61

66

70

75

79

84

88

93

97

102

106

111

115

120

124

129

133

138

142

147

151

156

HD

[D]

V3B

V4

V1A

V1B

V2

V3A

(2288)

0

(2288)

0

1130

1160

1190

1010

1040

1070

1100

1220

1250

1280

1310

1340

1370

1400

1430

HD of this chart indicates the actual CXD3406GA load timing.

The numbers at the output pulse transition points indicate the count at the MCKO rise from the fall of HD.

The HD fall period should be between approximately 2.9 to 9.5µ

s

(when the drive frequency is 18MHz). This chart shows a period

of 115ck (6.4µ

s). Internal SSG is at this timing.

Chart-10 Horizontal Direction Timing Chart

MODE

Draft/AF1/AF2 mode

Applicable CCD image sensor

∑

ICX252/262

≠ 38 ≠

CXD3406GA

Chart-11 High-Speed Phase Timing Chart

MODE

Applicable CCD image sensor

∑

ICX252/262

HD

HD'

CKI

CKO

ADCLK

MCKO

H1

H2

RG

XSHP

XSHD

XRS

172

52

1

HD' indicates the HD which is the actual CXD3406GA load timing.

The phase relationship of each pulse shows the logical position relationship. For the actual output waveform, a delay is added

to each pulse.

The logical phase of ADCLK can be specified by the serial interface data.

≠ 39 ≠

CXD3406GA

Chart-12 Vertical Direction Sequence Chart

MODE

Draft

Frame

Draft

Applicable CCD image sensor

∑

ICX252/262

VD

V1A

V1B

V2

V3A

V3B

V4

SUB

Mechanical shutter

Exposure time

CCD OUT

MODE

SMD

SHD

Close

Open

AB

C

EE

F

0

0

000

3

3

0

0

01

01

01

01

01

00

00

01

01

050h

050h

050h

050h

050h

000h

000h

050h

050h

AB

C

D

E

F

This chart is a driving timing chart example of electronic shutter normal operation.

Data exposed at D includes blooming component. For details, see the CCD image sensor Data Sheet.

The CXD3406GA does not generate the pulse to control mechanical shutter operation.

The switching timing of the drive mode and the electronic shutter data is not the same.

≠ 40 ≠

CXD3406GA

CCD Signal Processor Block Serial Interface Control

The CXD3406GA's CCD signal processor block basically loads the CCD signal processor block serial interface

data sent in the following format at the rising edge of SEN2, and the setting values are then reflected to the

operation 6 ADCLKI clocks after that.

CCD signal processor block serial interface control requires clock input to ADCLKI in order to load and reflect

the serial interface data to operation, so this should normally be performed when the timing generator block is

in the normal operation mode.

00

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

SSI2

SCK2

SEN2

There are four categories of CCD signal processor block serial interface data: standby control data, PGA gain

setting data, OB clamp level setting data, and input pulse polarity setting data.

Note that when data from multiple categories is loaded consecutively, the data for the category loaded last is

valid and data from other categories is lost. When transferring data from multiple categories, raise SEN2 for

each category and wait until the setting value 6 ADCKLI clocks after that has been reflected to operation, then

transmit the next category.

The detail of each data are described below.

Standby Control Data

Data

D00

D01

to

D03

D04

to

D14

D15

Symbol

TEST

CTG

FIXED

STB

Function

Test code

Category switching

--

Standby control

Data = 0

Data = 1

Set to 0.

D01 to D03 CTG

Set to All 0.

Normal operating mode

Standby mode

Data

D00

D01

to

D03

D04

to

D05

D06

to

D15

Symbol

TEST

CTG

FIXED

GAIN

Function

Test code

Category switching

--

PGA gain setting data

Data = 0

Data = 1

Set to 0.

D01 to D03 CTG

Set to All 0.

See D06 to D15 GAIN.

PGA Gain Setting Data

≠ 41 ≠

CXD3406GA

Data

D00

D01

to

D03

D04

to

D11

D12

to

D15

Symbol

TEST

CTG

FIXED

OBLVL

Function

Test code

Category switching

--

OB clamp level setting data

Data = 0

Data = 1

Set to 0.

D01 to D03 CTG

Set to All 0.

See D12 to D15 OBLVL.

OB Clamp Level Setting Data

Data

D00

D01

to

D03

D04

to

D12

D13

to

D15

Symbol

TEST

CTG

FIXED

POL

Function

Test code

Category switching

--

Input pulse polarity setting data

Data = 0

Data = 1

Set to 0.

D01 to D03 CTG

Set to All 0.

Set to All 0.

Input Pulse Polarity Setting Data

≠ 42 ≠

CXD3406GA

Detailed Description of Each Data

Shared data: D01 to D03 CTG [Category]

Of the data provided to the CXD3406GA by the CCD signal processor block serial interface, the CXD3406GA

loads D04 and subsequent data to each data register as shown in the table below according to the combination

of D01 to D03 .

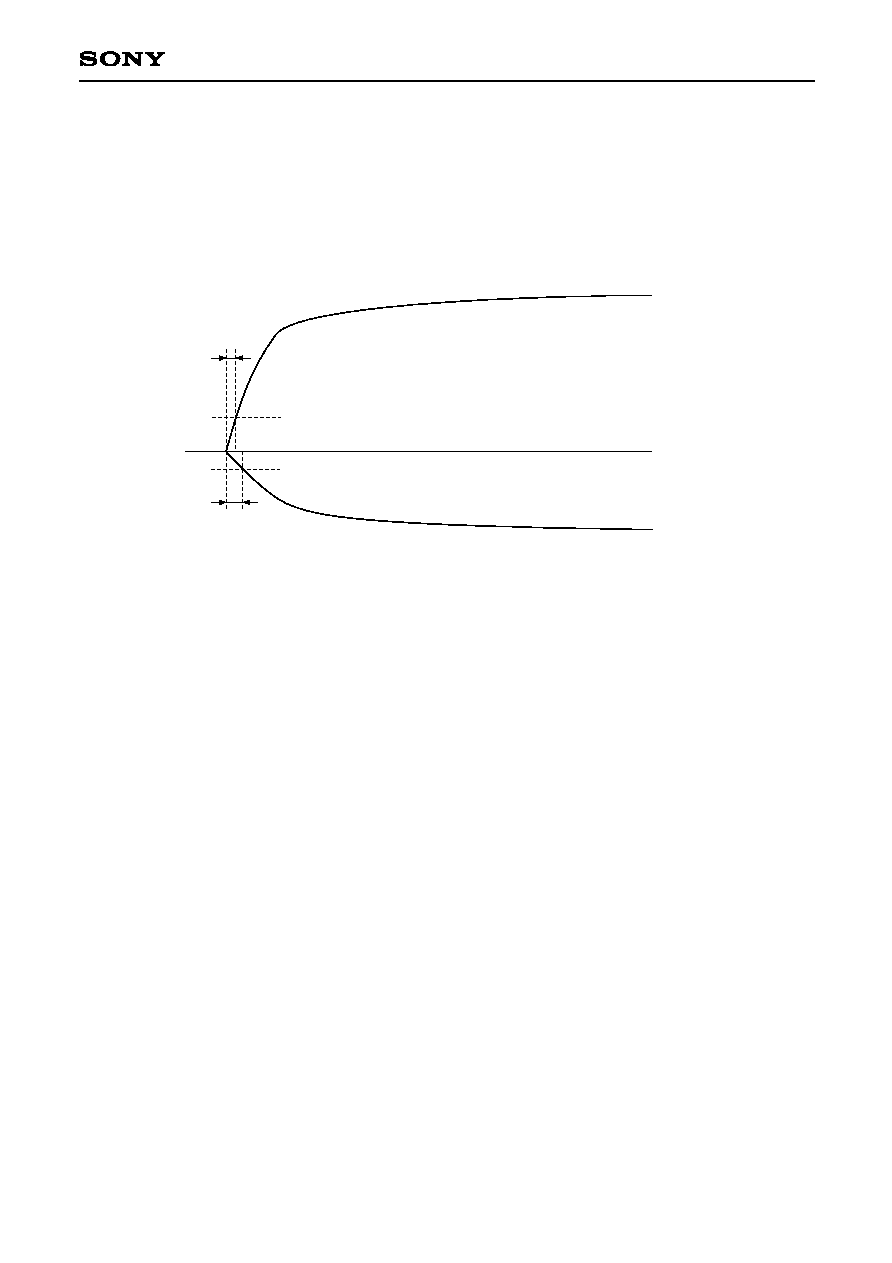

PGA gain setting data: D06 to D15 GAIN [PGA gain]

The CXD3406GA can set the programmable gain amplifier (PGA) gain from ≠6dB to +42dB in 1024 steps by

using PGA gain setting data D06 to D15 GAIN.

The PGA gain setting data is expressed as shown in the table below using D06 to D15 GAIN.

D01

0

0

0

0

1

D02

0

0

1

1

X

D03

0

1

0

1

X

Description of operation

Loading to standby control data register

Loading to PGA gain setting data register

Loading to OB clamp level setting data register

Loading to input pulse polarity setting data register

Access prohibited

Standby control data: D15 STB [Standby]

The operating mode of the CCD signal processor block is switched as follows. When the CCD signal processor

block is in standby mode, only the serial interface is valid.

D15

0

1

Description of operation

Normal operating mode

Standby mode

MSB

LSB

D06

D07

D08

D09

D10

D11

D12

D13

D14

D15

1

1

0

0

C

0

1

1

0

0

1

1

3

GAIN is expressed as 1C3h .

For example, when GAIN is set to "000h", "080h", "220h", "348h" and "3FFh", the respective PGA gain setting

values are ≠6dB, 0dB, +20dB, +34dB and +42dB.

≠ 43 ≠

CXD3406GA

OB clamp level setting data: D12 to D15 OBLVL [OB clamp level]

The CXD3406GA can set the OPB clamp output value from 0 to 60LSB in 4LSB steps by using CCD signal

processor block control data D12 to D15 OBLVL.

The OPB clamp output setting data is expressed as shown in the table below using D12 to D15 OBLVL.

MSB

LSB

D12

D13

D14

D15

0

1

1

0

6

OBLVL is expressed as 6h .

For example, when OBLVL is set to "0h", "1h", "8h" and "Fh", the respective OPB clamp output setting values

are 0LSB, 4LSB, 32LSB and 60LSB.

≠ 44 ≠

CXD3406GA

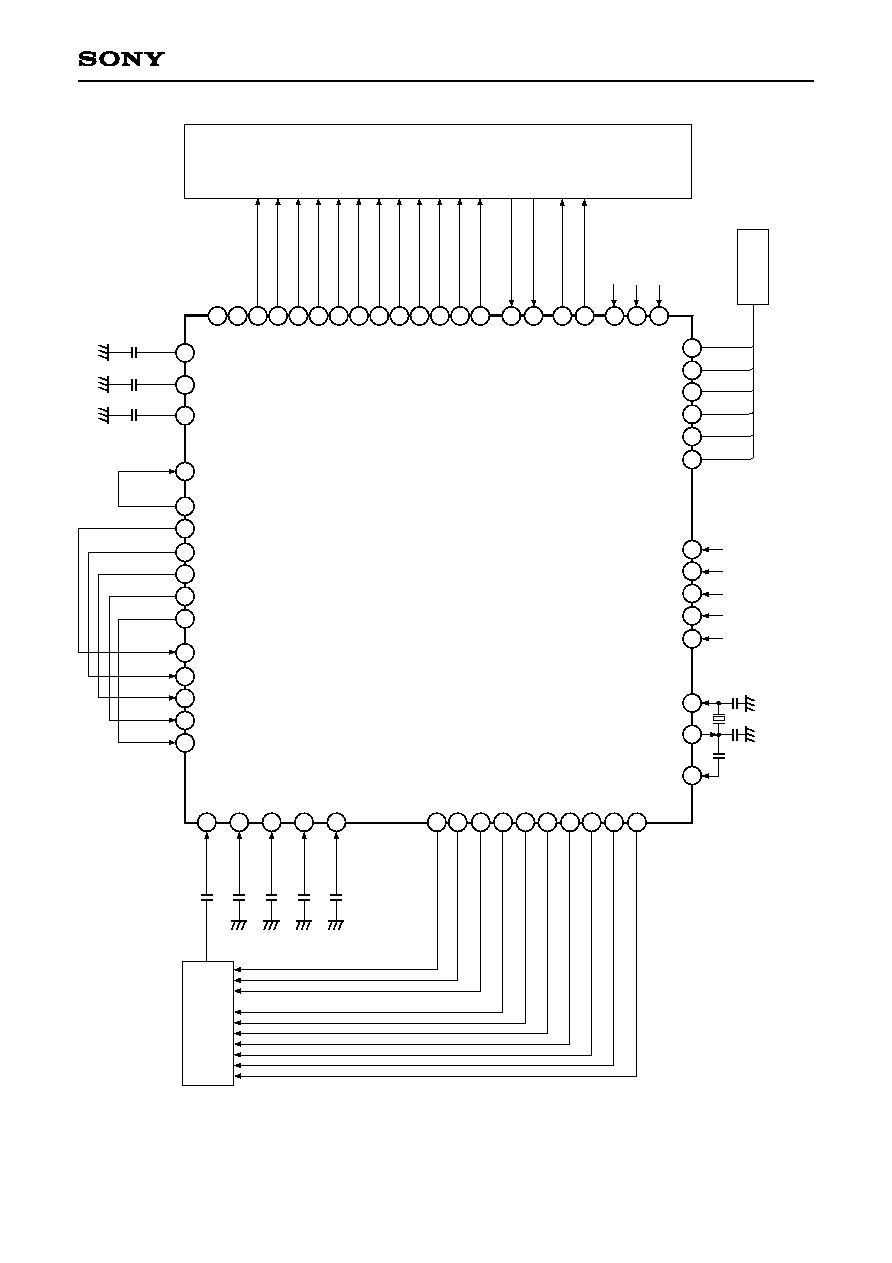

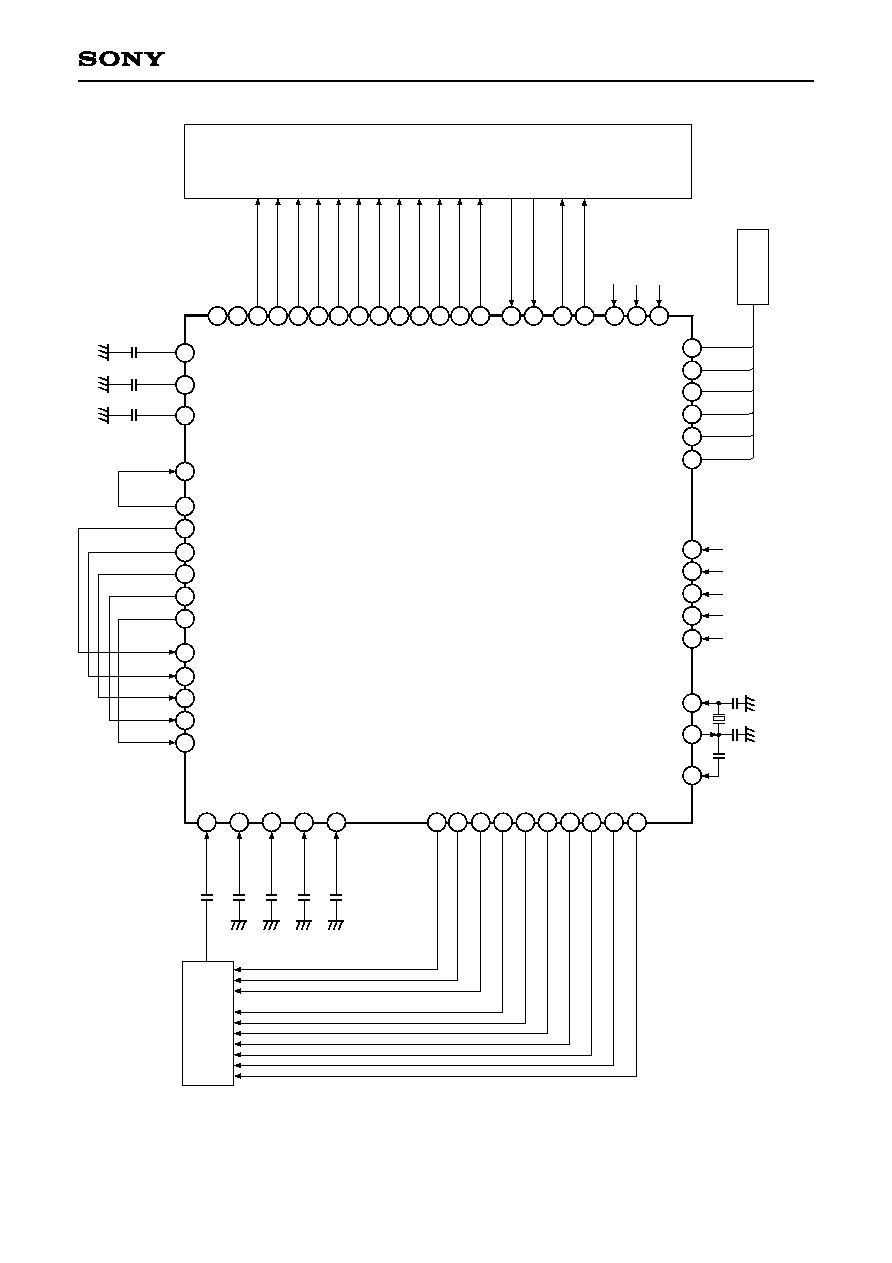

Application Circuit Block Diagram

SEN2

SCK2

SSI2

F9

F8

F7

G2

G3

G9

G8

G7

H2

H1

G1

B7

A7

C6

B3

A1

A2

B2

B1

C3

C2

C1

D3

D2

D1

E1

J2

K2

M2

N2

N9

M9

M8

N8

L8

M4

N5

L5

K8

J9

J8

C8

C7

D8

D7

C9

N4

L5

N7

N6

A3

B4

A4

M1

N1

L2

B5

C4

L1

J1

K1

A5

M7

M3

H3

CCD

ICX252/262

TG/CDS/PGA/ADC

CXD3406GA

Controller

SSI1

SEN1

SCK1

TEST5

TEST4

TEST3

TEST2

TEST1

OSCO

CKI

OSCI

D1

VD

HD

D0 (LSB)

Signal

Processor

Bloc

k

D2

NC

NC

D3

D4

D5

D6

D7

D8

D9 (MSB)

MCK

O

CK

O

SSGSL

SNCSL

RST

WEN

ID

0.1µF

C7

XSHPI

XSHDI

PBLKI

CLPDMI

CLPOBI

XSHP

XSHD

PBLK

CLPDM

CLPOB

ADCLK

ADCLKI

0.1µF

C8

0.1µF

C9

1µF

C1

1µF

CCDIN

CCDOUT

390pF

C2

390pF

C3

240pF

C4

H1

H2

RG

V1A

V1B

V2

V3A

V3B

V4

SUB

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility fo

r

any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same

.

This block diagram illustrates connections with each circuit

block, and is not an actual circuit diagram. See the CCD

image sensor data sheet for an example of specific circuit

connections with the CCD image sensor.

≠ 45 ≠

CXD3406GA

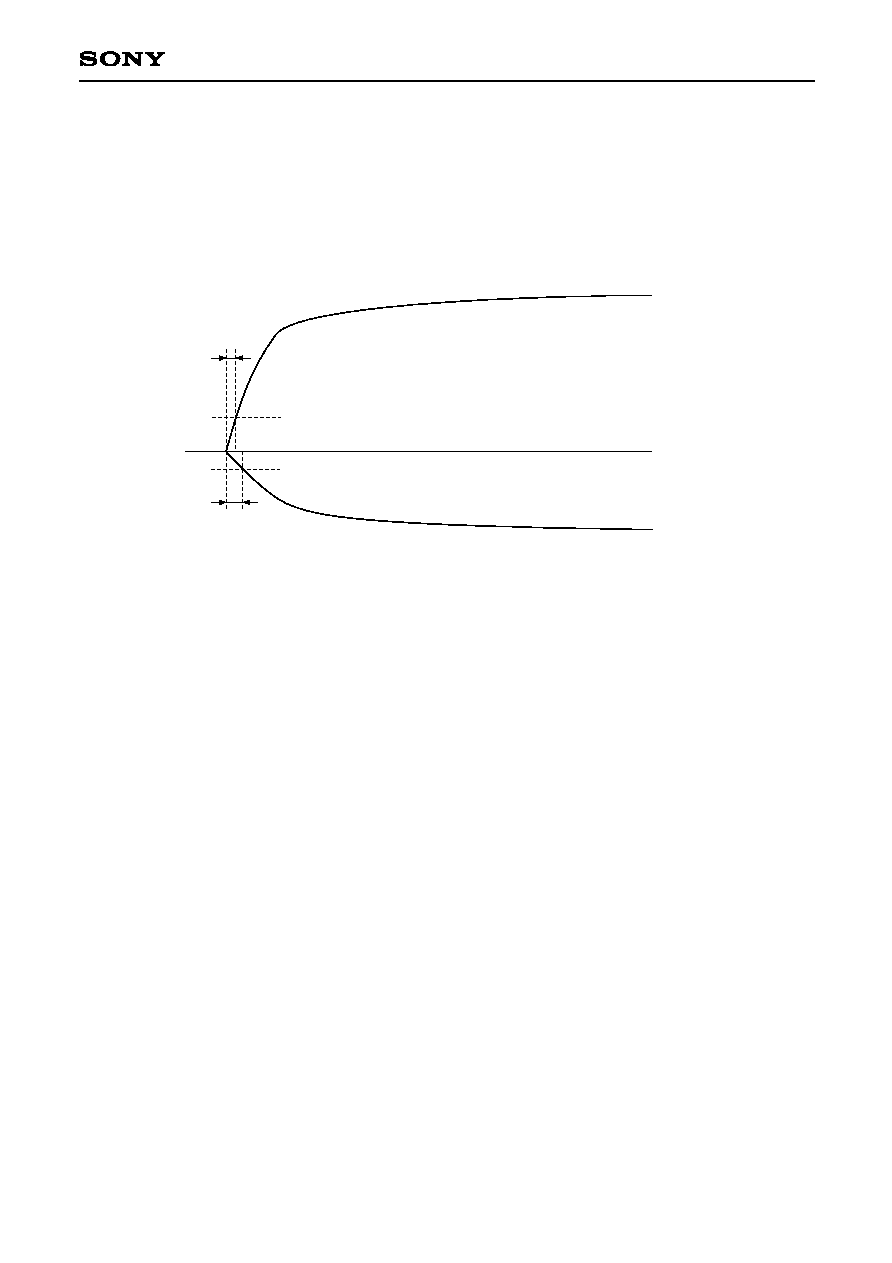

Notes on Operation

1. Be sure to start up the timing generator block VL and VH pin power supplies at the timing shown in the

figure below in order to prevent the SUB pin of the CCD image sensor from going to negative potential. In

addition, start up the timing generator block V

DD1

, V

DD2

, V

DD3

, V

DD4

and V

DD5

pin and CCD signal processor

block DV

DD1

, DV

DD2

, AV

DD1

, AV

DD2

, AV

DD3

, AV

DD4

and AV

DD5

pin power supplies at the same time either

before or at the same time as the VH pin power supply is started up.

2. Reset the timing generator block and CCD signal processor block during power-on. The timing generator

block is reset by inputting the reset signal to the RST pin. The CCD signal processor block is reset by

initializing the serial data.

3. Separate the timing generator block V

DD1

, V

DD2

, V

DD3

, V

DD4

and V

DD5

pins from the CCD signal processor

block DV

DD1

, DV

DD2

, AV

DD1

, AV

DD2

, AV

DD3

, AV

DD4

and AV

DD5

pins.

Also, the ADC output driver stage is connected to the dedicated power supply pin DV

DD1

. Separating this

pin from other power supplies is recommended to avoid affecting the internal analog circuits.

4. The difference in potential between the timing generator block V

DD4

pin supply voltage 3 V

DD

c and the CCD

signal processor block DV

DD1

, DV

DD2

, AV

DD1

, AV

DD2

, AV

DD3

, AV

DD4

and AV

DD5

pin supply voltages 1 V

DD

e,

2 V

DD

f and 3 V

DD

g should be 0.1V or less.

5. The timing generator block and CCD signal processor block ground pins should use a shared ground which

is connected outside the IC. When the set ground is divided into digital and analog blocks, connect the

timing generator block ground pins to the digital ground and the CCD signal processor block ground pins to